# Customer Care Solutions NPL-2 Series Cellular Phones

# 6 - Baseband Description and Troubleshooting

# **Table of Contents**

| B                                 | Pa |

|-----------------------------------|----|

| Description                       | N  |

| Baseband Top-level Description    |    |

| Baseband Block Diagram            |    |

| NPL-2 Baseband Feature List       |    |

| Environmental Specifications      |    |

| Normal and Extreme Voltages       |    |

| Temperature Conditions            |    |

| Humidity                          |    |

| Frequencies in Baseband           |    |

| Printed Wire Board (PWB)          |    |

| Infrared Interface (IrDA)         |    |

| Baseband Architecture             |    |

| Baseband Core                     |    |

| Universal Phone Processor (UPP)   |    |

| Universal Energy Management (UEM) |    |

| External Flash and External SRAM  |    |

| Energy Management                 |    |

| Power Supply Modes                |    |

| Battery BL-4C                     | 1  |

| RTC Capacitor                     | 1  |

| Power Distribution                | 1  |

| DC Characteristics                | 1  |

| Charging                          | 1  |

| Audio Circuitry                   |    |

| Audio Block Diagram               | 1  |

| Earpiece                          | 1  |

| Microphone                        | 1  |

| Integrated Hands-free (IHF)       | 1  |

| Audio Accessory Receive Path      |    |

| Audio Control Signals             | 1  |

| Acoustics                         | 1  |

| Earpiece Acoustic                 | 1  |

| IHF Speaker Acoustic              |    |

| Microphone Acoustic               |    |

| Vibra Motor                       |    |

| Audio Modes                       | 2  |

| Hand Portable Mode                | 2  |

| Integrated Hands-free Audio Mode  | 2  |

| Headset Audio Mode                |    |

| Loopset Audio Mode                |    |

| External Hands-free Audio Mode    |    |

| User Interface                    |    |

| LCD Module                        |    |

| Baseband LCD Interface            |    |

| DC Characteristics                |    |

|                                                         | Page |

|---------------------------------------------------------|------|

| Description                                             | No.  |

| Current Consumption                                     | 24   |

| Maximum Ratings                                         | 24   |

| AC Characteristics                                      | 24   |

| Rest Timing                                             | 25   |

| Display Power On/Off Sequence                           | 26   |

| LED Power Supply                                        | 26   |

| Keypad                                                  | 27   |

| SIM Interface                                           | 28   |

| BB-RF Interface                                         | 29   |

| Digital Signals between BB and RF                       | 29   |

| Analog Signals between BB and RF                        | 30   |

| Voltage Regulators in BB for RF                         | 31   |

| System Connector Interface                              | 33   |

| System Connector                                        | 33   |

| Accessory Control Interface (ACI)                       | 34   |

| Signal Flow on ACI line ACI-ASIC accessory inserted     | 35   |

| Signal Flow on ACI line Non ACI-ASIC accessory inserted | 36   |

| FBUS                                                    | 36   |

| VOUT (Accessory Voltage Regulator)                      | 37   |

| HookInt                                                 | 38   |

| Charging                                                | 38   |

| DC-Plug                                                 | 38   |

| VCHAR Pins of System Connector                          | 38   |

| Voltages and Currents                                   | 39   |

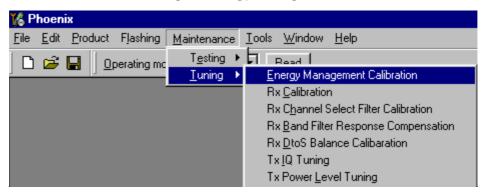

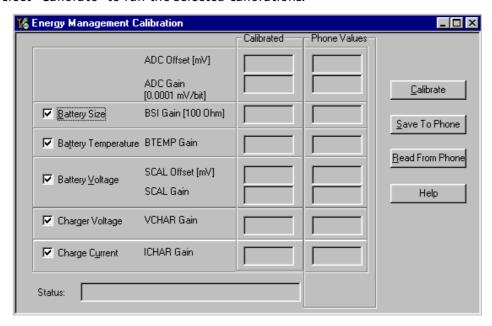

| Baseband Calibration                                    | 39   |

| BB Calibration Limits                                   | 40   |

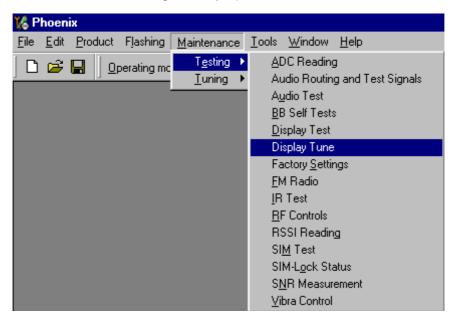

| Baseband Tuning Operations                              | 40   |

| Energy Management Tuning                                | 40   |

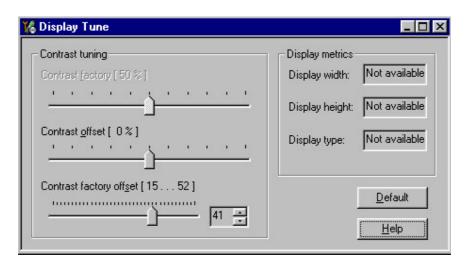

| LCD Contrast Tuning                                     | 41   |

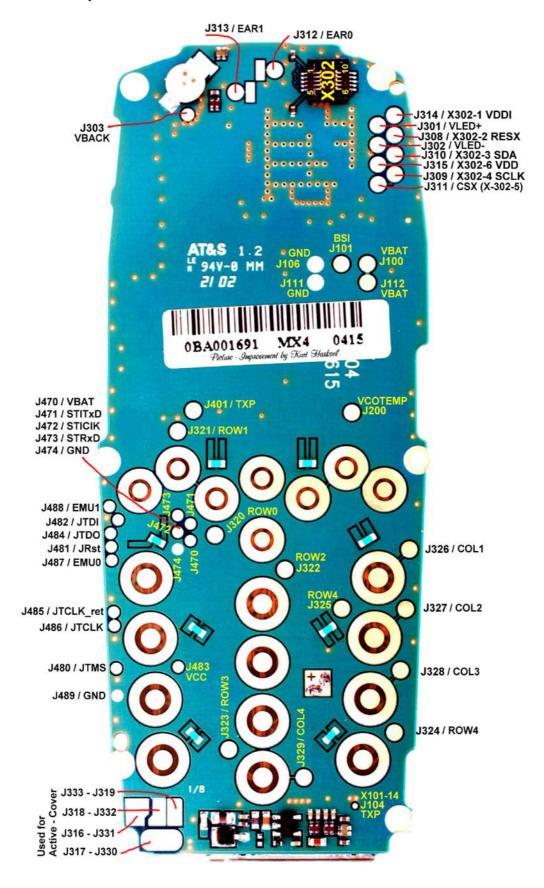

| Baseband Testpoints                                     | 44   |

| List and Description                                    | 44   |

| Testpoints on Bottom-side                               | 45   |

| Testpoints on Top-side                                  | 46   |

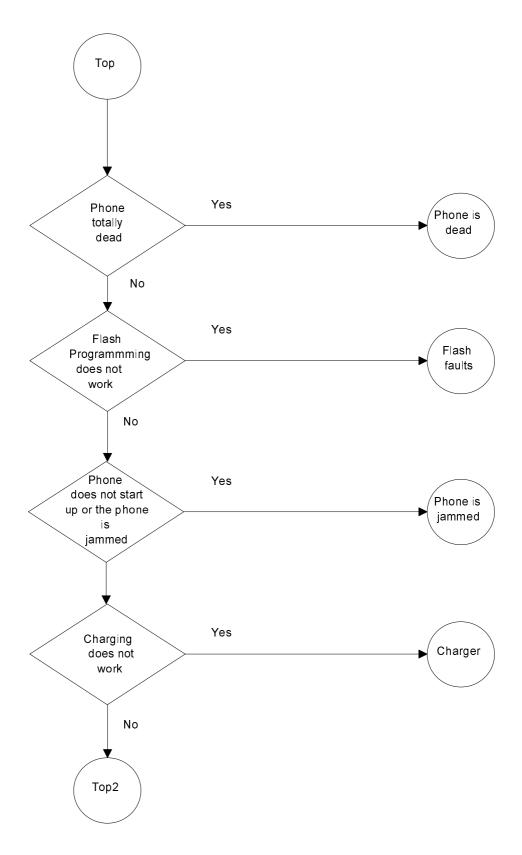

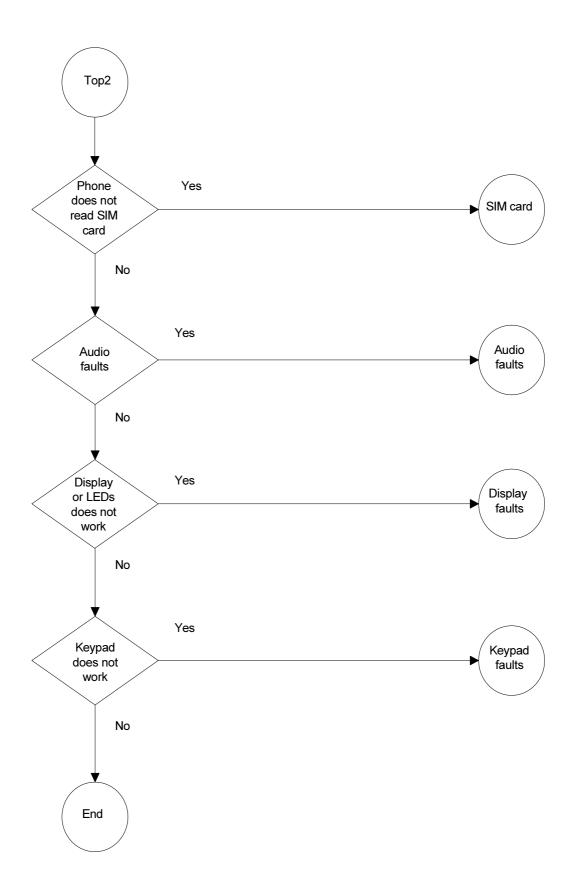

| Baseband Troubleshooting                                | 47   |

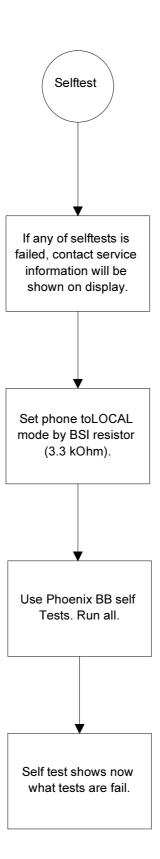

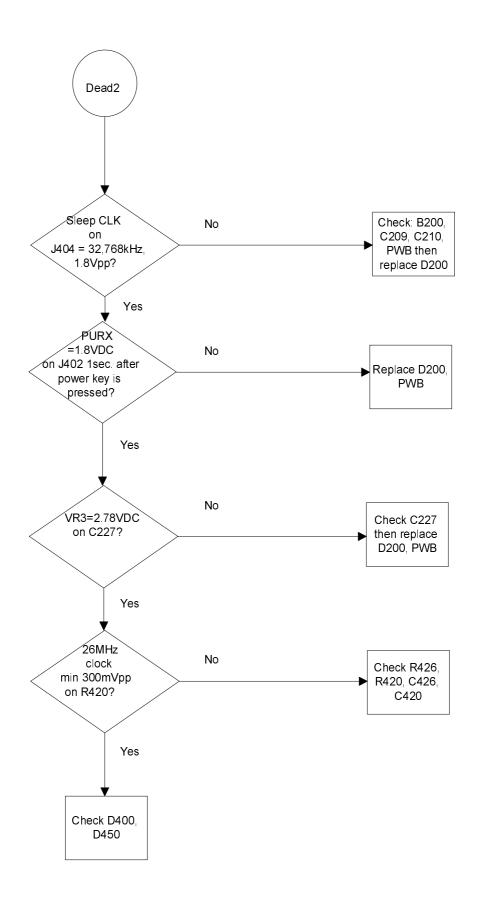

| Top Level Flowchart                                     | 48   |

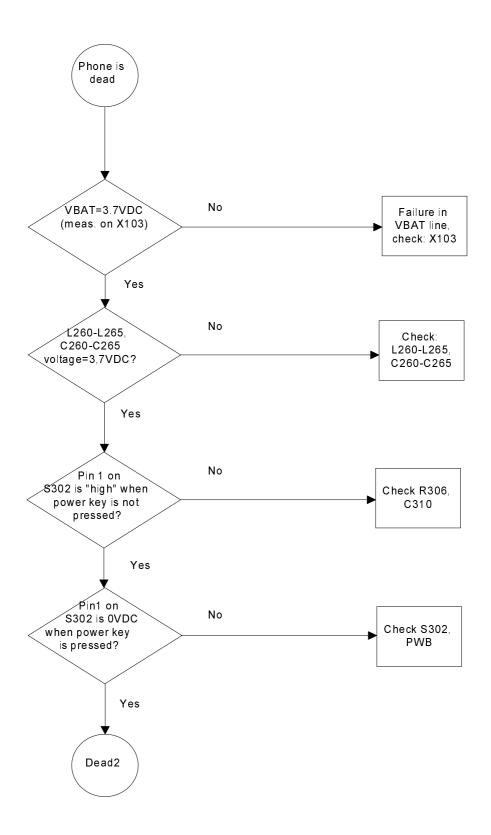

| Phone is Dead                                           | 50   |

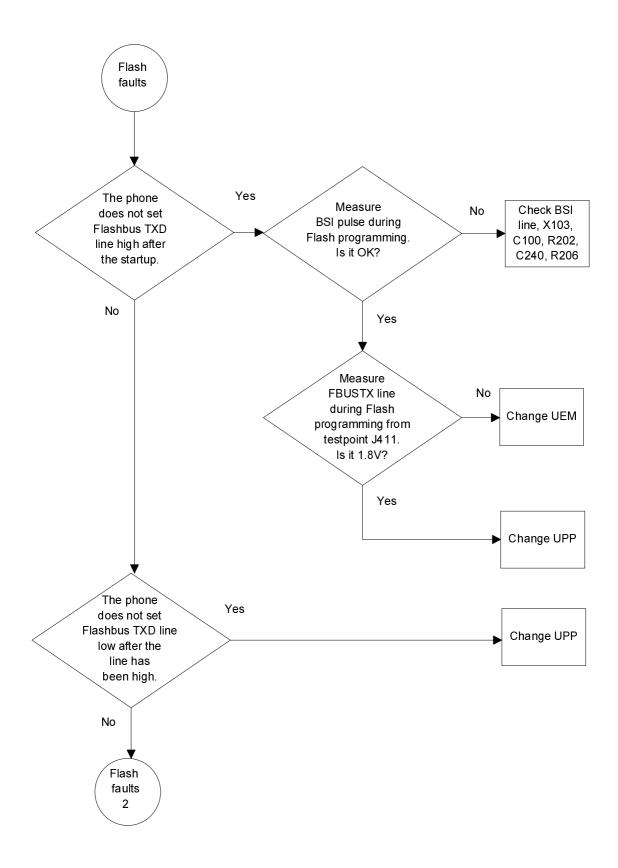

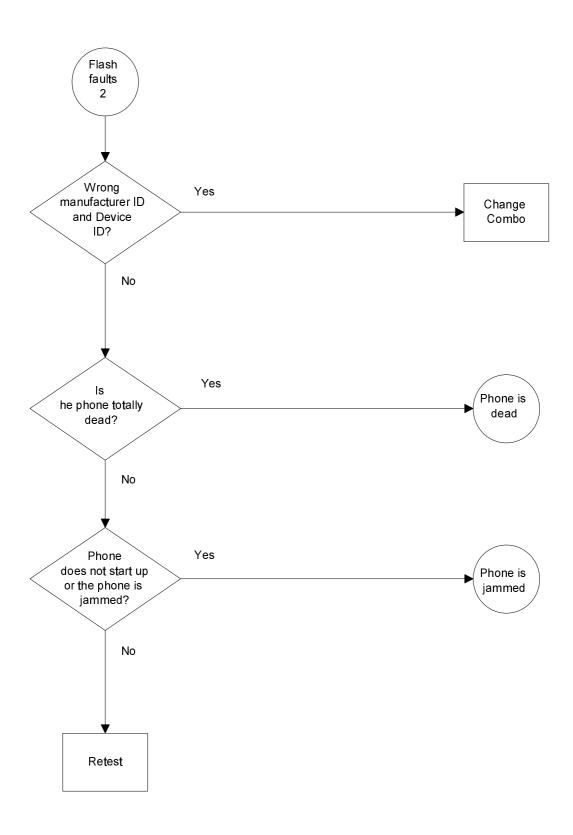

| Flash Faults                                            | 52   |

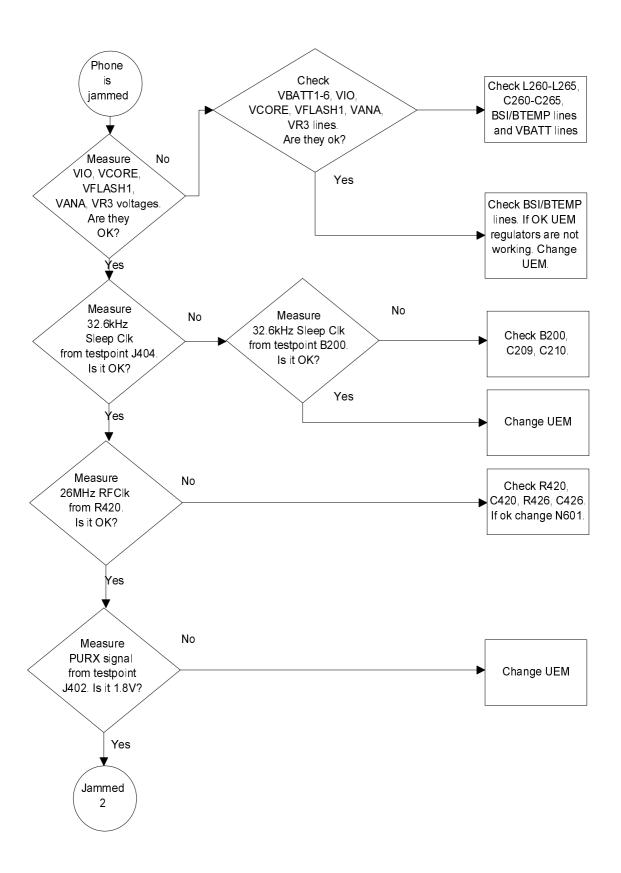

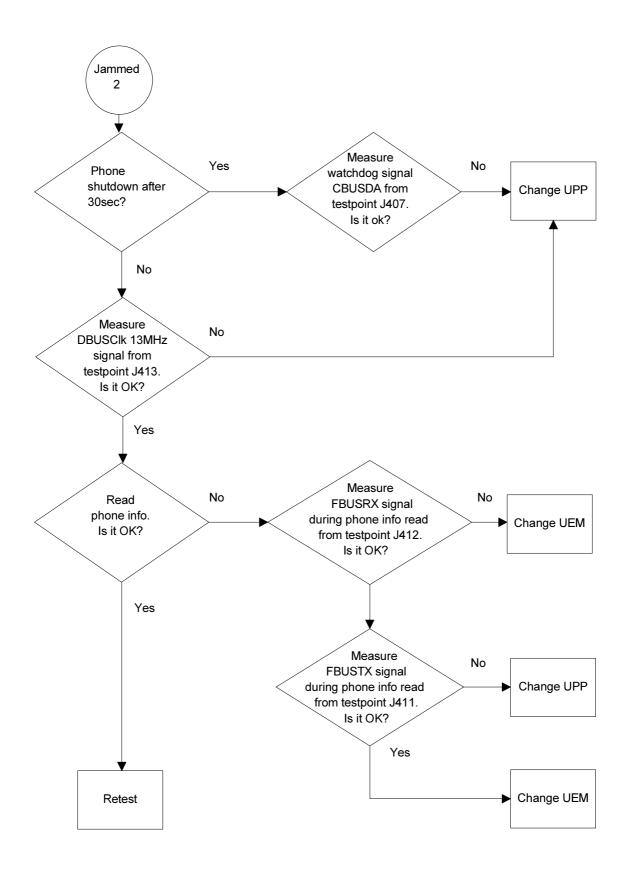

| Phone is Jammed                                         | 54   |

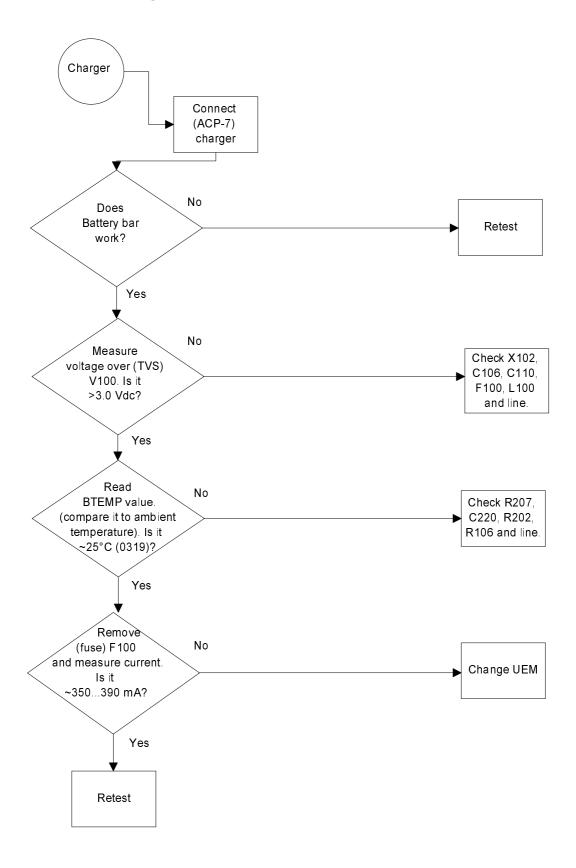

| Phone does not Charge                                   | 56   |

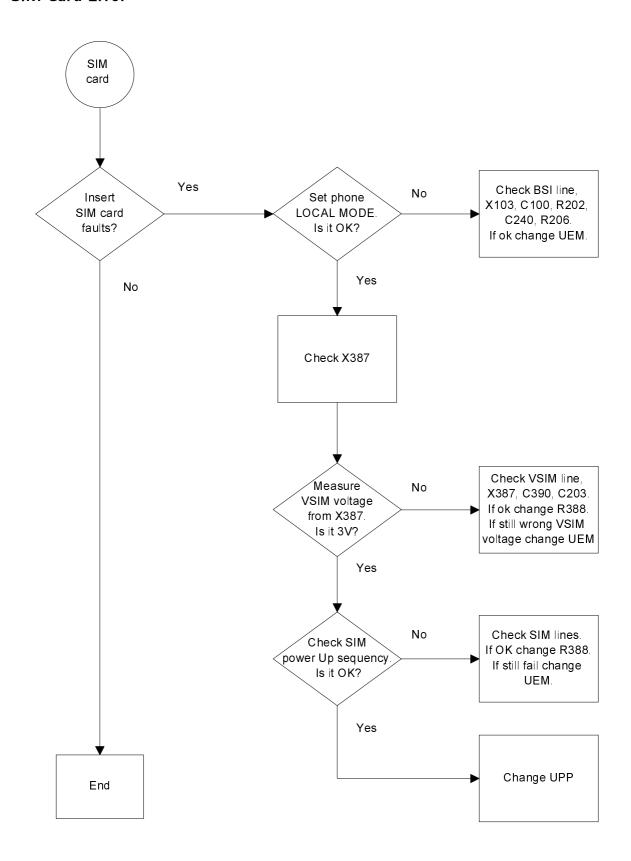

| SIM Card Error                                          | 57   |

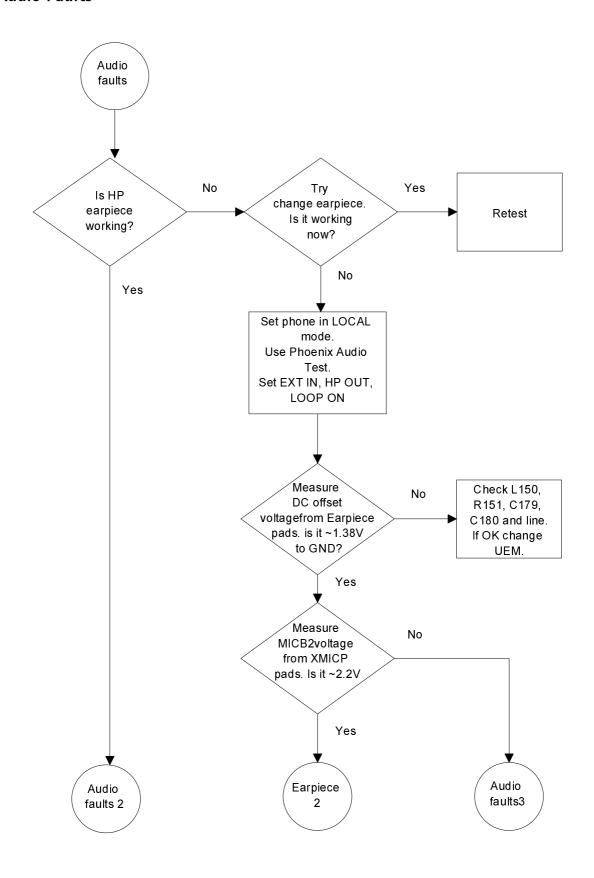

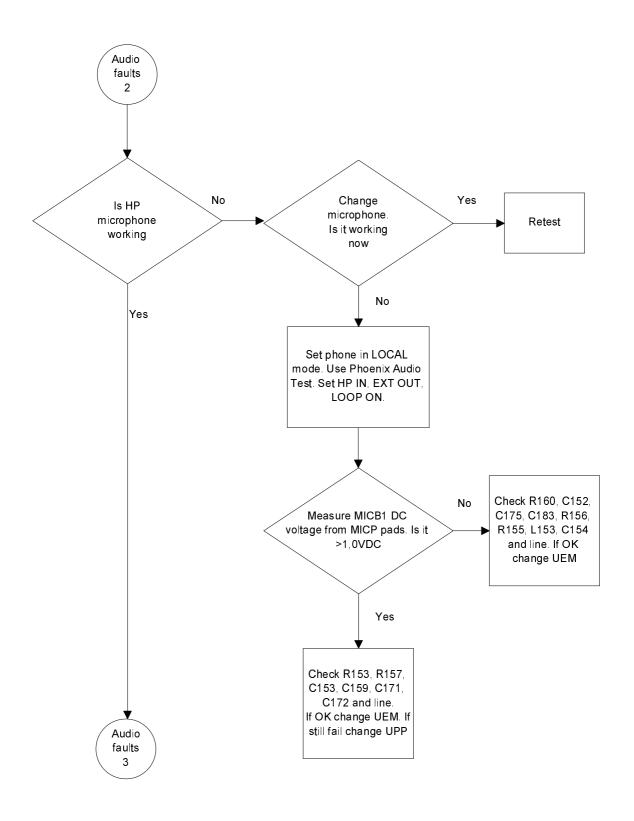

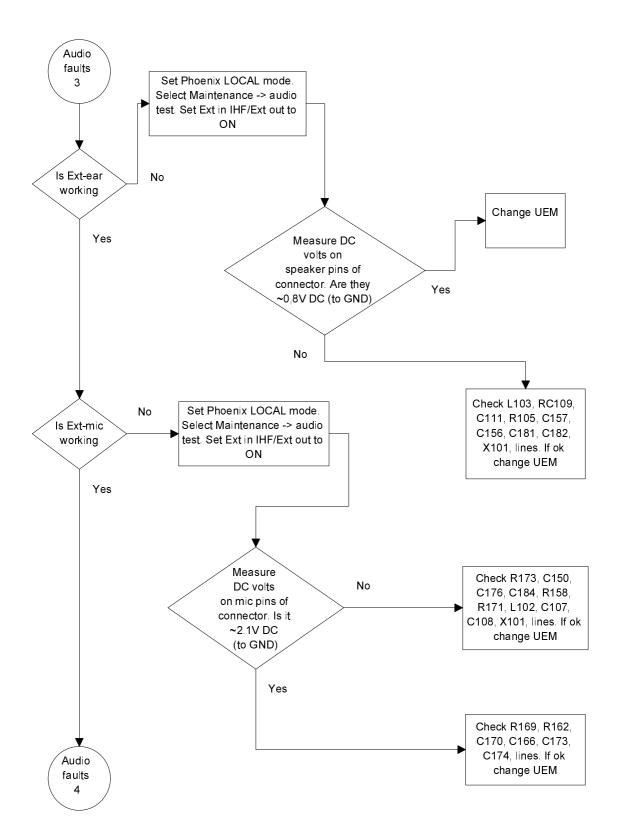

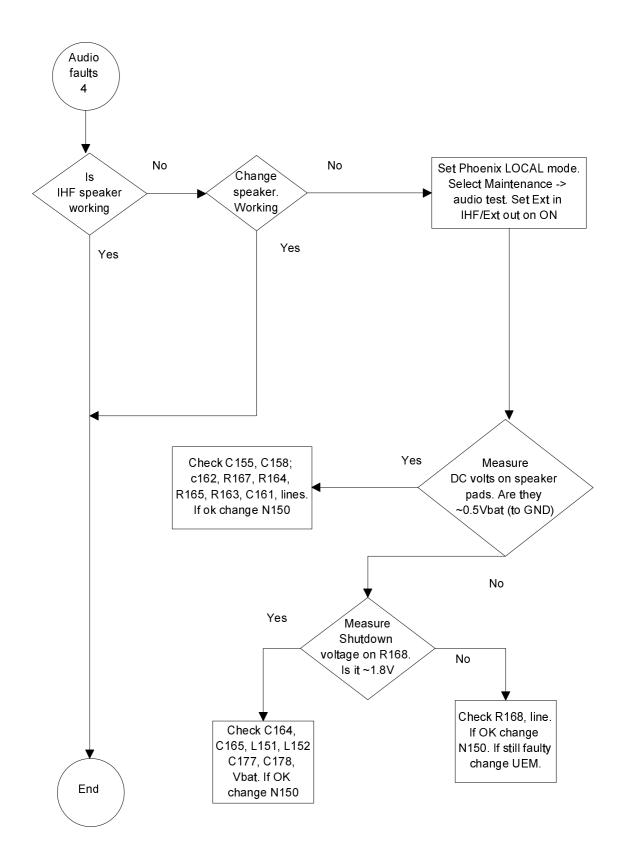

| Audio Faults                                            | 58   |

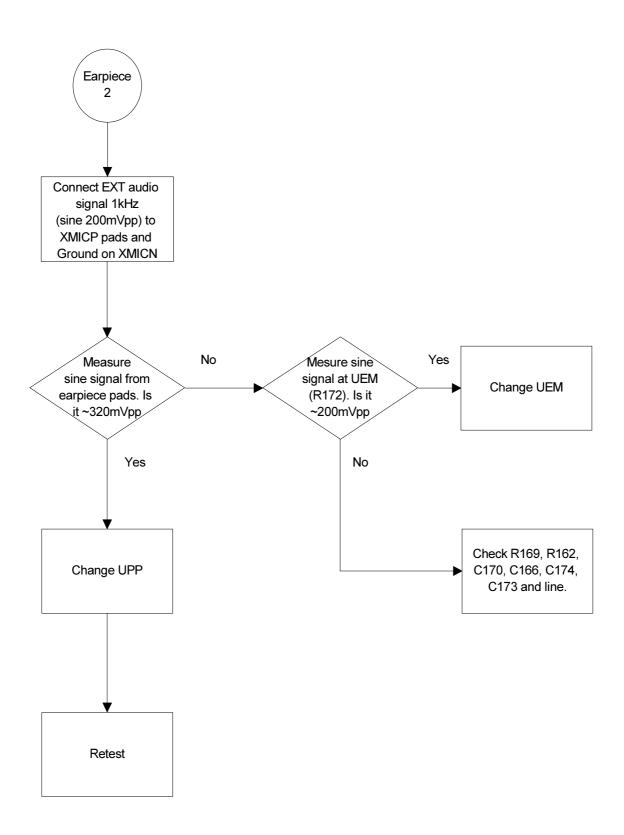

| Earpiece Fault                                          | 62   |

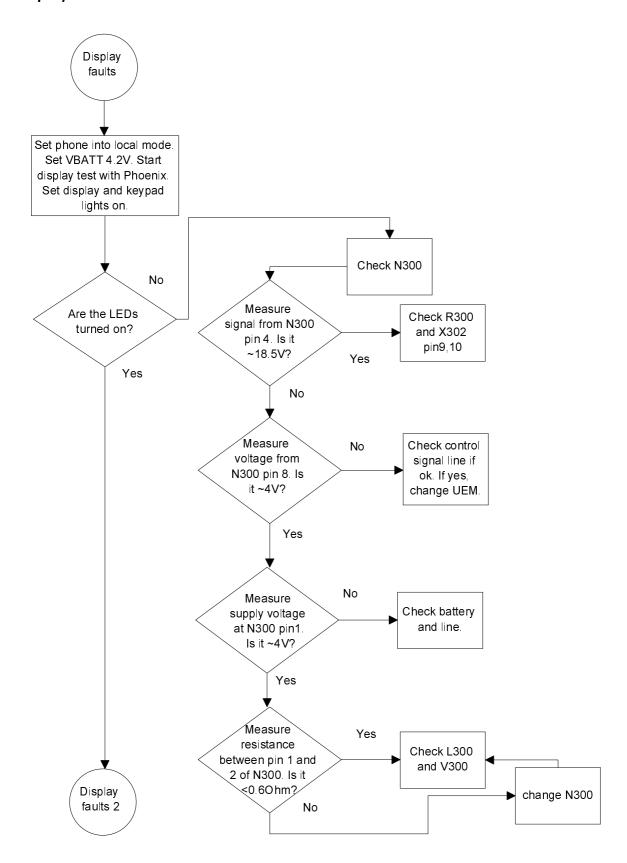

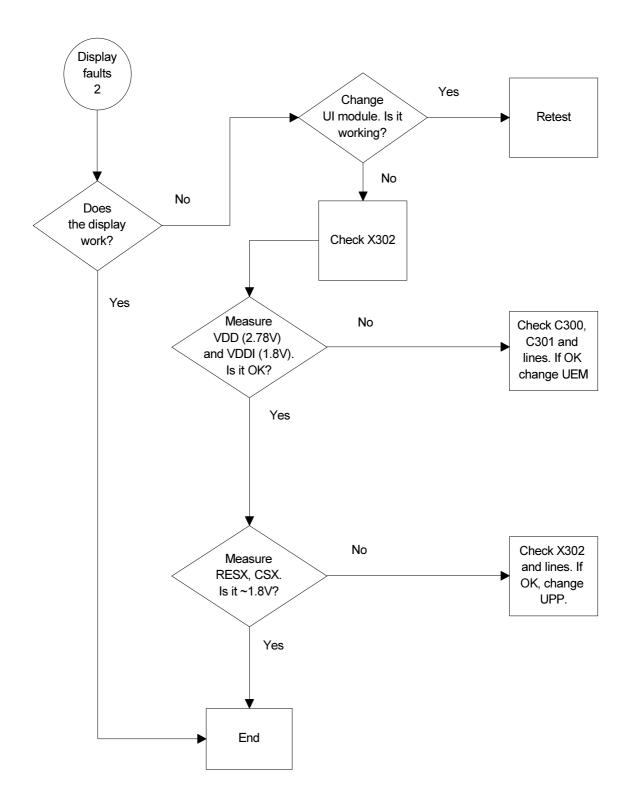

| Display Fault                                           | 63   |

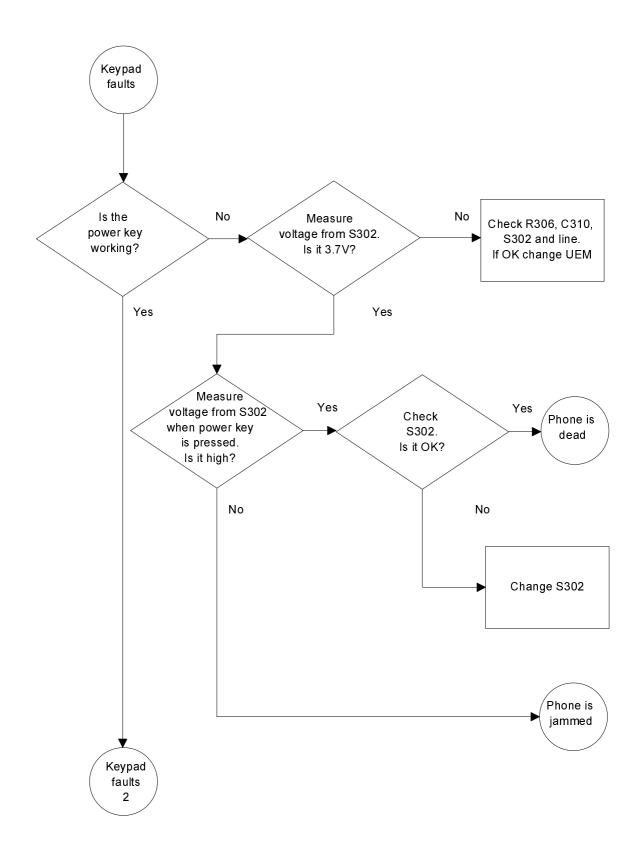

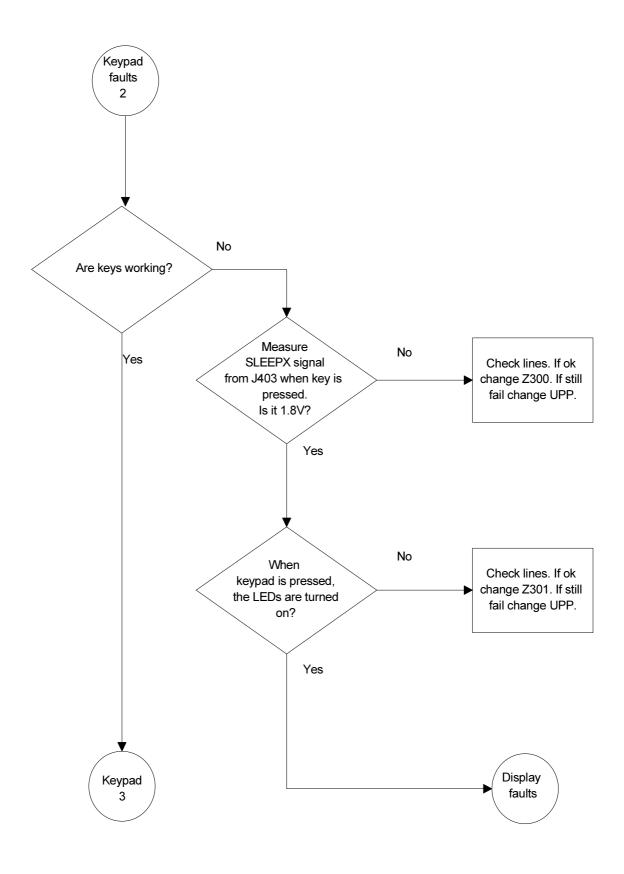

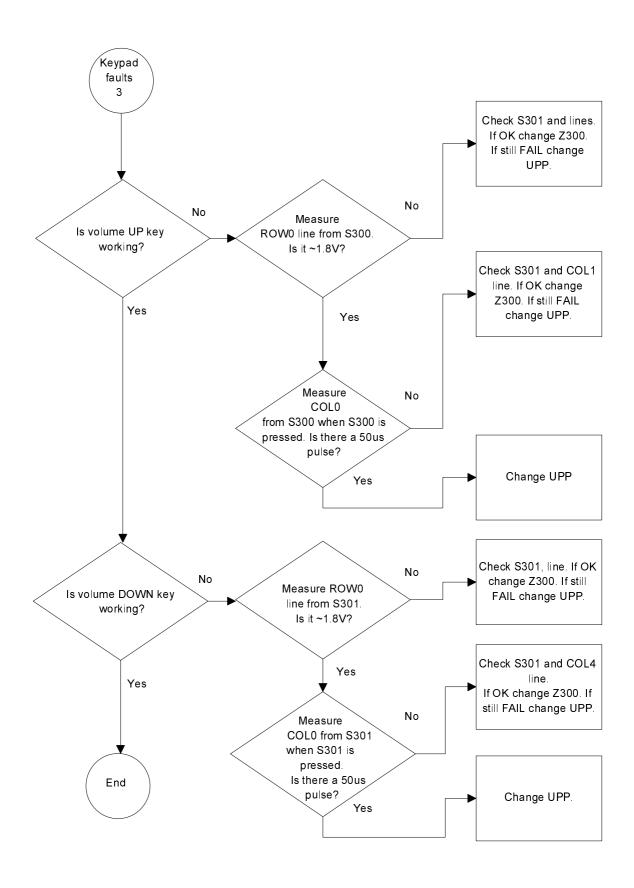

| Keypad Fault                                            | 65   |

| Selftest Fault                                          | 68   |

|                     |                                                                          | Page     |

|---------------------|--------------------------------------------------------------------------|----------|

|                     | Description                                                              | No.      |

| List of Fig         | gures                                                                    |          |

| Figure 1            | Baseband block diagram                                                   | 5        |

| Figure 2            | UEM state diagram                                                        | 10       |

| Figure 3            | Baseband power distribution                                              | 14       |

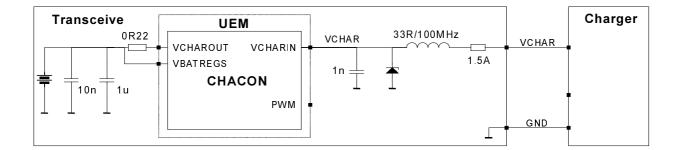

| Figure 4            | Charging configuration                                                   | 16       |

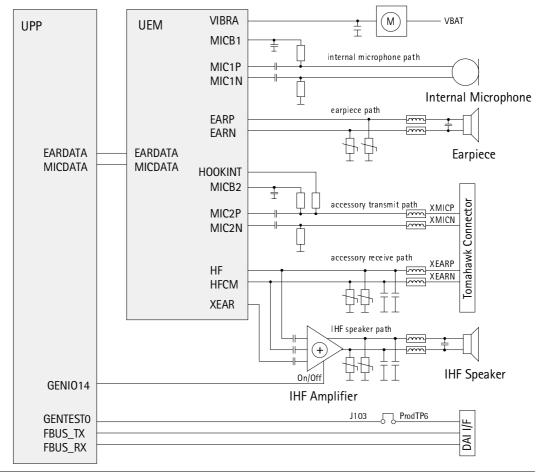

| Figure 5            | Audio block diagram                                                      | 17       |

| Figure 6            | Earpiece implementation                                                  | 19       |

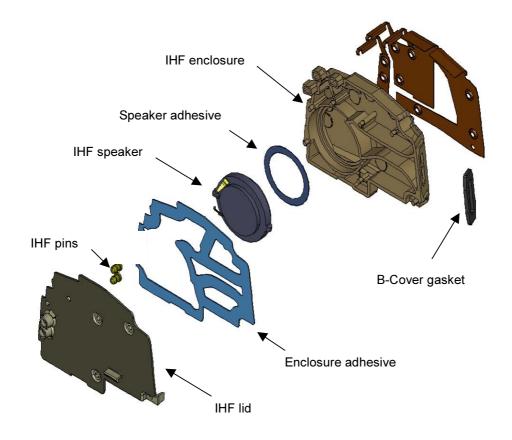

| Figure 7            | Exploded view of antenna assembly                                        | 20       |

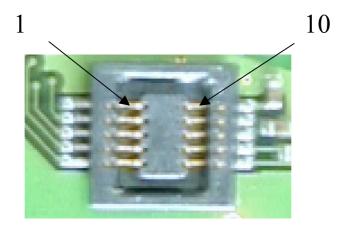

| Figure 8            | LCD connector                                                            | 23       |

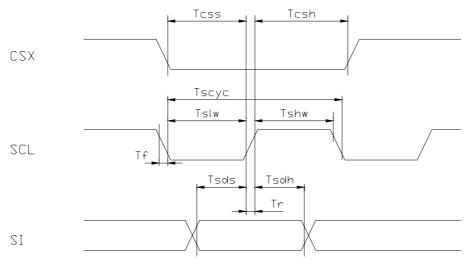

| Figure 9            | Write characteristics                                                    | 24       |

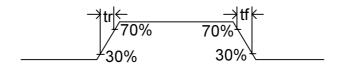

| Figure 10           | Rise and fall time in input and output                                   | 25       |

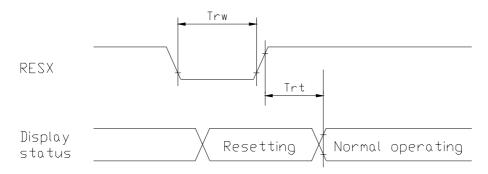

| Figure 11           | Reset timing                                                             | 25       |

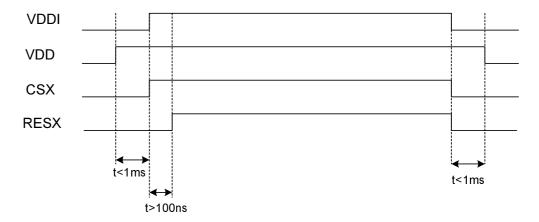

| Figure 12           | Power on/off sequence                                                    | 26       |

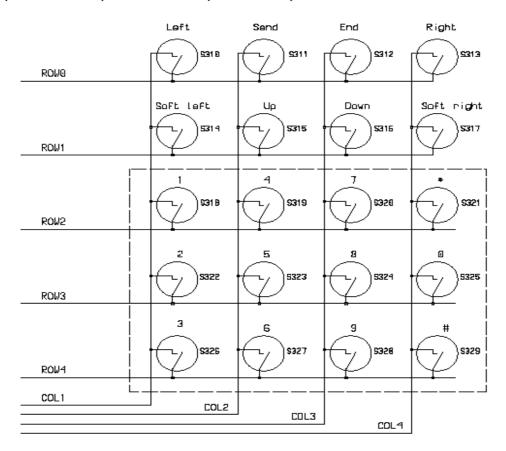

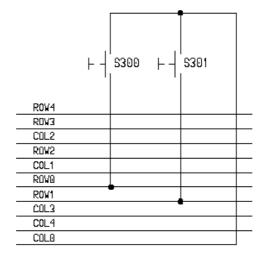

| Figure 13           | NPL-2 keypad                                                             | 27       |

| Figure 14           | Side (volume) keys                                                       | 27       |

| Figure 15           | UPP, UEM and SIM connections                                             | 29       |

| Figure 16           | Pop Port system connector                                                | 33       |

| Figure 17           | Principle schematics of ACI accessory and engine                         | 35       |

| Figure 18           | ACI communication                                                        | 35       |

| Figure 19           | Signal flow on ACI line                                                  | 36       |

| Figure 20           | Accessory power supply diagram                                           | 37       |

| List of Ta          | hles                                                                     |          |

|                     |                                                                          | _        |

| Table 1             | Frequency list                                                           | 7        |

| Table 2             | UEM regulator outputs                                                    | 15       |

| Table 3             | Handportable mode audio routing                                          | 21       |

| Table 4             | IHF mode audio routing                                                   | 21       |

| Table 5             | Headset mode audio routing                                               | 21       |

| Table 6             | Loop set mode audio routing                                              | 22       |

| Table 7<br>Table 8  | External hands-free mode audio routing  LCD interface DC characteristics | 22<br>23 |

|                     |                                                                          |          |

| Table 9<br>Table 10 | LCD interface current consumption  LCD interface maximum ratings         | 24<br>24 |

| Table 11            | <u> </u>                                                                 |          |

| Table 12            | AC characteristics  Rise and fall times in input and output of display   | 24       |

| Table 13            |                                                                          | 25<br>25 |

| Table 14            | Reset timingRF-BB interface digital signals                              | 25<br>29 |

| Table 15            | RF-BB interface analog signals                                           | 30       |

| Table 16            | Voltage supplies and references                                          | 31       |

| Table 17            | System connector interface description                                   | 33       |

| Table 18            | Voltage levels                                                           | 36       |

| Table 19            | FBUS interface                                                           | 37       |

| Table 20            | Accessories power supply                                                 | 37       |

| Table 21            | Voltage levels Hook Int                                                  | 38       |

| Table 22            | Charger input voltage levels                                             | 39       |

| Table 23            | System connector interface signals                                       | 39       |

| Table 24            | BB Calibration limits                                                    | 40       |

| Table 25            | NPL-2 test points                                                        | 44       |

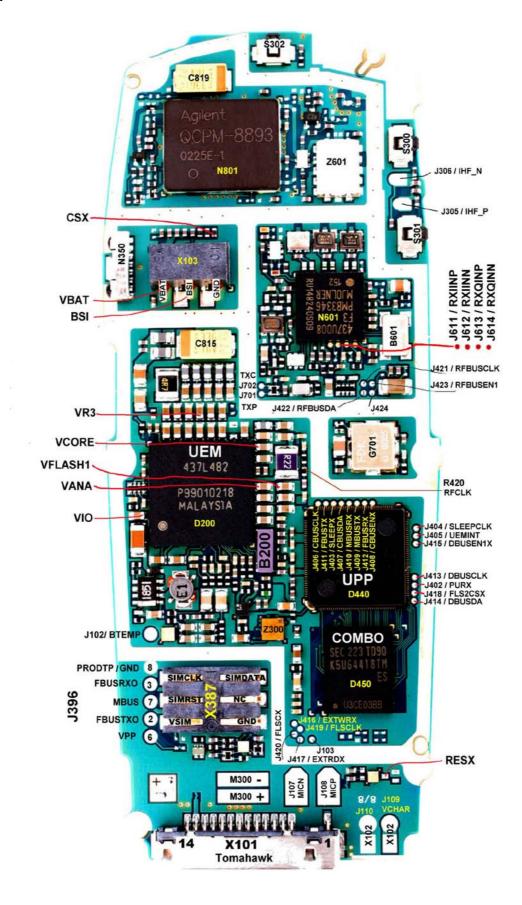

# **Baseband Top-Level Description**

Product NPL-2 is a hand portable EGSM900, GSM1800, GSM-1900 DCT-4 generation phone for the smart classic segment.

The NPL-2 Baseband consists of the DCT4 common Baseband chipset having some product specific blocks of its own, such as pop-port system connector (also unofficially known as "Tomahawk"), IHF, IrDA and a color display.

The Baseband engine consists basically of two major ASIC's.

- The UEM is the Universal Energy Management IC. It includes the analog audio circuits, the charge control and voltage regulators.

- The UPP is the Universal Phone Processor and contains DSP, MCU and some internal memory.

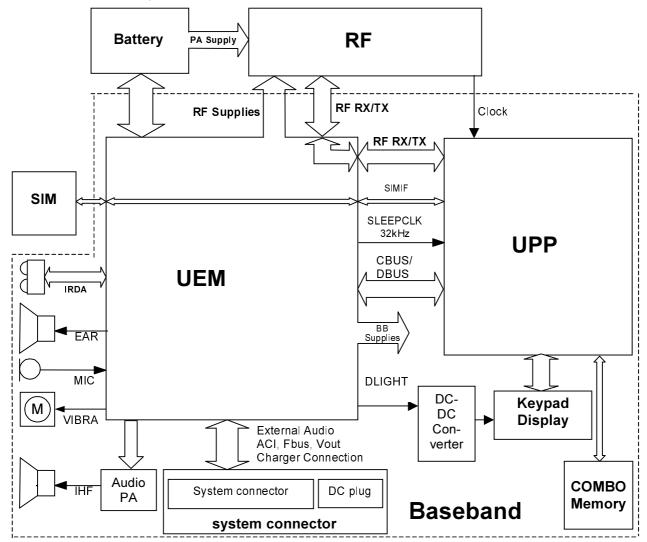

# **Baseband Block Diagram**

The below system block shows the main BB function blocks.

Figure 1: Baseband Block Diagram

# NPL-2 Baseband Feature List

Hardware characteristics:

- Single PWB design

- Universal Phone Processor UPP8Mv2.x with 8Mbit internal SRAM

- Additional external 4Mbit SRAM and 64MBit FLASH memory in one single package (called Combo).

- Universal Energy Management ASIC "UEM K"

- GSM triple band (900/1800/1900 MHz)

- BL-4C battery

- Internal antenna assembled on IHF container

- Small SIM, supporting 1.8 & 3.0V

- Integrated infrared module (IrDA)

- Internal vibra motor

#### UI features:

- 130x130 pixel color display, 4096 colors

- Standard keypad with 4-way navigation key, two soft keys and two side keys

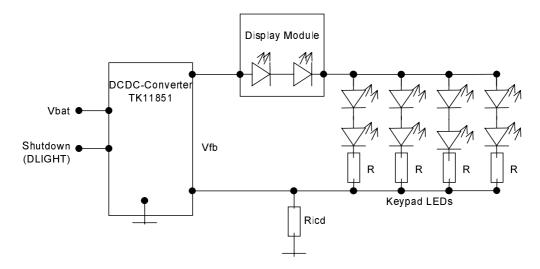

- Illumination concept is based on a DC-DC converter

- Display: two white LED's

- Keypad: eight blue LED's

- Polyphonic ringing tones (MIDI)

- Internal hands-free

# **Environmental Specifications**

# Normal and Extreme Voltages

Following voltages are assumed as normal and extreme voltages for used battery:

Nominal voltage: 3.6 V

Lower extreme voltage: 3.1 V

Higher extreme voltage (fast charging): 4.4 V

# **Temperature Conditions**

Operational temperature range (all specifications met within this range)

-10°C..+55°C

Functional temperature range (Reduced performance) -30°C..+70°C Storage temperature range: -30°C..+85°C

Frequency depends on SW

# **Humidity**

Relative humidity range is 5...95%.

The BB module is not protected against water. Condensed or splashed water may cause interim or permanent phone malfunction.

Any submerge of the phone most likely causes permanent damage.

# Frequencies in Baseband

There are several clock frequencies at the baseband part. Below table lists all available frequencies. The asynchronous and diagnostic busses are not included.

Flash **UPP UEM** Frequency Context SIM Comment 40 MHz Χ Memory clock Χ 26 MHz RF clock Χ 13 MHz DBUS, RFBusClk Χ Χ 3.25 MHz SIM Χ MIN. FREQ. RFConvClk Χ Up to 1 MHz Χ **ESTIMATION** CBUS Χ Χ 1 MHz 32 kHz Sleep clock Χ 1.2 kHz ACI Χ Χ

Χ

Table 1: Frequency list

# Printed Wire Board (PWB)

1.625 / 6.5

Characteristics of the PWB

- Single PWB

- 1.2 mm, 8 layer board

- Double sided assembled

- Through holes, vias and buried vias are possible

Display IF

The PWB is prepared for I-Line under filling of UEM, UPP and the Flash (64 Mbit and 128 Mbit).

# Infrared Interface (IrDA)

NPL-2 supports data connectivity via an Infrared link. An IR module is integrated into the phone, connected to the IR interface of the UPP ASIC. NPL-2 uses the Rohm RPM960-H7 module.

# **Baseband Architecture**

# **Baseband Core**

# **Universal Phone Processor (UPP)**

Main characteristics of the used UPP are:

- DSP by Texas Instruments, LEAD3 PH2+ Megacell 16 bit DSP core, 32 bit I/F max. speed 200 MHz.

- MCU based on ARM/Thumb 16/32 bit RISC MCU core max. speed 50 MHz

- Internal 8 Mbit SRAM (PDRAM)

- General purpose USARTs

- SIM card interface

- Accessory interface (ACI)

- Interface control for: keypad, LCD, audio and UEM control

- IrDA interface

- Handling of RF-BB interface

The UPP is housed in a 144-pin uBGA package (12x12mm, 0.8mm pitch).

In NPL-2 the UPP is clocked by a 26MHz frequency from the RF-chip "Mj

This 26MHz-clock frequency is internally sliced down by UPP to 13MHz. This frequency is then inside UPP multiplied to different frequencies, e.g. 145MHz for the DSP core.

UPP can operate on 4 different voltages; 1.05,1.3,1.5 and 1.8V. The voltage can be programmed "on the fly" by the SW. For example in standby-mode, 1.3V is used for power saving, but in active-mode (i.e. call) the voltages is increased to 1.8V to get maximum performance.

# **Universal Energy Management (UEM)**

NPL-2 uses the UEM version so called "UEM K". UEM K is a die shrinked version of standard UEM's, but with the same functionality.

Main characteristics of UEM's are:

- ACI support

- Audio codec

- 11 Channel A/D converter

- Auxiliary A/D converter

- Real time logic

- 32 kHz crystal oscillator

- SIM interface and drivers

- Security logic

- Storage of IMEI code

- Buzzer and vibra motor drivers

- 2 LED drivers

- IR Interface

- Voltage references needed for analogue blocks

- Charging function

- Baseband regulators

- RF regulators

- RF interface converters

The UEM is housed in a 168-pin uBGA package (12x12mm, 0.8mm pitch).

#### **External Flash and External SRAM**

The Combo-Memory is a multi chip package memory which combines 64Mbit (4Mx16) muxed burst multi bank Flash and 4Mbit muxed CMOS SRAM. These two dies are stacked on each other in one package. The functionality of the Flash memory is the same, as it is known from generic BB4.0 products.

The combo is supplied by single 1.8V for read, write and erase operation.

This Combo memory is housed in a 48-ball TBGA type with a 0.5mm ball pitch. The outer dimensions are 10x8mm and the thickness is 1.1 mm.

# **Energy Management**

The energy management of NPL-2 is based on BB 4.0 architecture. A so called semi fixed battery (BL-4C) supplies power primarily to UEM ASIC and the RF PA. UEM includes several regulators to supply RF and baseband. It provides the energy management including power up/down procedure.

If the main battery is not present, a capacitor maintains backup power supply for the Real Time Clock (RTC) part of UEM.

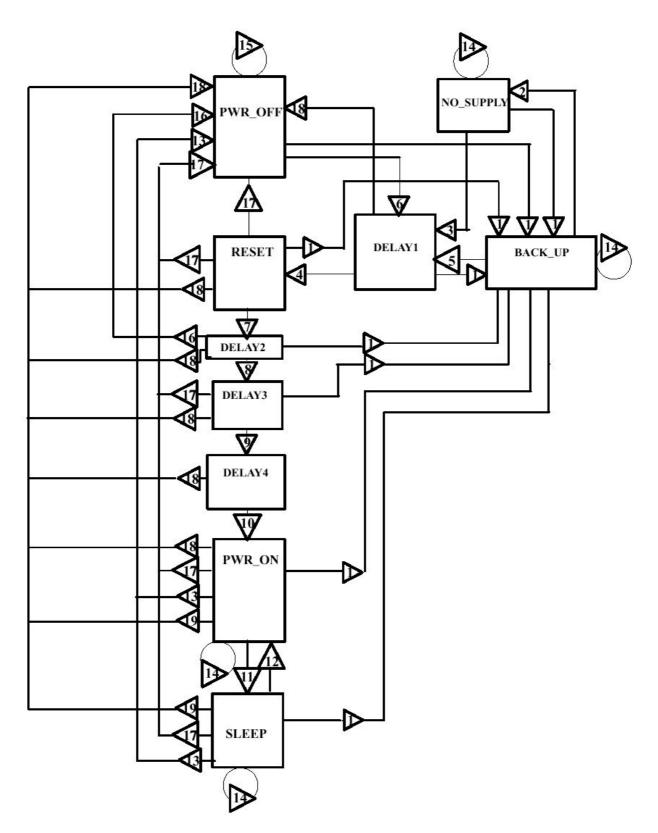

#### **Power Supply Modes**

The functional behavior of the UEM can be divided into 7 different states. Since the UEM controls the regulated power distribution of the phone, each of these states affects the general functionality of the phone:

- No supply

- Backup

- Power off

- Reset

- Power on

- Sleep

- Protection

Figure 2 UEM state diagram

6 - Baseband Description and Trouble-

The text below explains the state diagram. The symbol '7' means that the voltage rises and ' $\mbox{'}$ ' that the voltage drops. ' $\mbox{--}$ ' Means the result of the conditions set on the left most side.

| $VBAT < V_{MSTR}$                 | and $VBACK > V\_BU_{COFF}$ | $ ightarrow$ BACK_UP         |

|-----------------------------------|----------------------------|------------------------------|

| $VBAT < V_{MSTR}$                 | and $VBACK < V_BU_{COFF}$  | $\rightarrow$ NO_SUPPLY      |

| VBAT 7 VMSTR+                     | and VBACK < V_BUcoff       | $\rightarrow$ DELAY1         |

| VBAT > VMSTR                      | and DELAY1 elapses         | $\rightarrow$ RESET          |

| VBAT <b>↗</b> V <sub>MSTR+</sub>  | and $VBACK > V_BUCOFF$     | $\rightarrow$ DELAY1         |

| PWRONX = '0'                      | or VCHAR                   | $\rightarrow$ DELAY1         |

| $VBAT > V_{COFF+}$                |                            | ightarrow DELAY2             |

| DELAY2 elapses                    |                            | $\rightarrow$ DELAY3         |

| VBAT > COFF+.                     | and DELAY3 elapses         | $\rightarrow$ DELAY4         |

| DELAY4 elapses                    |                            | $\rightarrow$ PWR_ON         |

| SLEEPX = '0'                      |                            | $\to SLEEP$                  |

| SLEEPX = '1'                      |                            | $\rightarrow$ PWR_ON         |

| VBAT 🗵 Vcoff                      | and $VBAT > V_{MSTR}$      | $\rightarrow$ PWR_OFF        |

| No change                         |                            |                              |

| $VBAT > V_{MSTR}$                 |                            | $ ightarrow$ Stay in PWR_OFF |

| PWRONX 7 detection during DELAY2  |                            | $\rightarrow$ PWR_OFF        |

| Watchdog elapses (approx. 100 (s) |                            | $\rightarrow$ PWR_OFF        |

| Thermal shutdown                  |                            | $\rightarrow$ PWR_OFF        |

| PwrKeyWatchdog (4 sec.) elapses   |                            | $\rightarrow$ PWR_OFF        |

The different states of the UEM are detailed in the sections below.

# No Supply

In the NO\_SUPPLY mode the UEM has no supply voltage (VBAT < V<sub>MSTR</sub> and VBACK < V\_BU<sub>COFF</sub>-). This mode is due to the fact that both the main battery and the backup battery are either disconnected or both discharged to a low voltage level.

The UEM will recover from NO\_SUPPLY into RESET mode if the VBAT voltage level rises above the  $V_{MSTR+}$  level by either reconnecting the main battery or charge it to such level.

# Backup

In BACK\_UP mode the main battery is either disconnected or has a low voltage level (VBAT  $< V_{MSTR-}$  and VBACK  $> V_{BU_{COFF+}}$ ).

The regulator VRTC that supplies the real time clock is disabled in BACK\_UP mode. Instead the unregulated backup battery voltage VBACK supplies the output of the VRTC. All other regulators are disabled and the phone has no functionality.

The UEM will recover from BACK\_UP mode into RESET mode if VBAT rises above V<sub>MSTR+</sub>.

#### Power Off

In order for the UEM to be in PWR\_OFF mode, it must have supply voltage (VBAT  $> V_{MSTR+}$ ).

The regulator VRTC regulator is enabled and supplying the RTC within the UEM. The UEM will enter RESET mode after a 20 ms delay whenever one of the below listed conditions is logically true:

- The power button is activated

- Charger connection is detected

- RTC alarm is detected

The UEM will enter PWR\_OFF from all other modes except NO\_SUPPLY and BACK\_UP if the internal watchdog elapses.

#### Reset

When the UEM enters RESET mode from PWR\_OFF mode the watchdog is enabled. If the VBAT fails to rise above the power-up voltage level  $V_{COFF+}$  (3.1 V) before the watchdog elapses, the UEM will enter PWR\_OFF mode. Otherwise after a 200 ms delay the regulator VFLASH1 will be enabled and after an additional delay of 500  $\mu$ s the regulators VANA, VIO, VCORE and VR3 will be enabled. All other regulators i.e. VFLASH2, VSIM, VR1, VR2 and VR4 - VR7 are software controlled and disabled by default. After an additional delay of 20 ms the UEM enters PWR\_ON mode.

# Power On

In PWR\_ON the UEM is fully functional in the sense that all internal circuits is powered up or can be by means of software. The UEM will enter PWR\_OFF mode if VBAT drops below  $V_{COOF}$  for a period of time longer than 5  $\mu$ s. The UEM will furthermore enter PWR\_OFF mode if either of the watchdogs Operational State Machine (approx. 100  $\mu$ s), Security (32 sec.) or Power Key (4 sec.) elapses or if any of the regulators triggers the thermal protection circuitry

#### Sleep

The UEM can be forced into SLEEP mode by the UPP by setting the input SLEEPX low for more than 60  $\mu$ s. This state is entered when the external UPP activity is low (phone in sleep) and thereby lowering the internal current consumption of the UEM. The regulator VANA is disabled and VR1 – VR7 are either disabled or in low quiescent mode.

From SLEEP the UEM enters PWR\_ON if SLEEPX goes high, PWR\_OFF mode if watchdog elapses or BACK\_UP mode if VBAT drops below V<sub>MSTR</sub>.

#### **Protection Mode**

The UEM has two separate protection limits for over temperature conditions, one for the charging switch and one for the regulators. The temperature circuitry measures the onchip temperature. In case of charging over temperature, the circuit turns the charging switch off. In case of over temperature in any of the regulators, the UEM powers off.

6 - Baseband Description and Trouble-

# Battery BL-4C

Product NPL-2 uses the so called "case-less" Li Ion battery BL-4C.

BL-4C battery capacity is 720mAh.

Main advantage of case-less battery types is the overall size, particular the thickness and the number of contact terminals.

This battery has a three-pin connector (BTEMP is not used). The battery does not support temperature measurement inside battery pack. In order to get temperature information of the battery, a NTC is mounted on the PWB within the BB area.

Ni based batteries are not supported by NPL-2.

The resistor value for battery size indication (BSI) is 68 kOhm.

# **RTC Capacitor**

To sustain the RTC when BL-4C is removed from the phone, a backup capacitor is used in NPL-2. This capacitor is soldered directly to the PWB. Its capacity is 0.01 mAh. This provides approx. 2.9 hours of backup time.

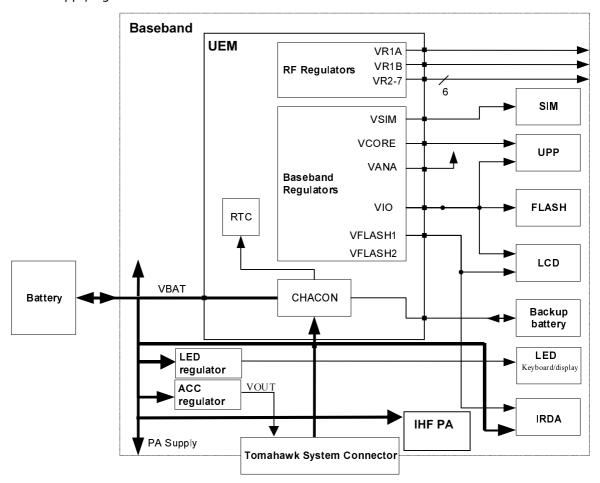

#### **Power Distribution**

Under normal conditions, the battery powers the baseband module. Individual regulators located within the UEM regulate the battery voltage **VBAT**. These regulators supply the different parts of the phone. 8 regulators are dedicated to the RF module of the phone, and 6 to the baseband module.

The **VSIM** regulator is able to deliver both 1.8V and 3.0V DC and thus supporting two different SIM technologies. A register internally in the UEM controls the output of VSIM and can be written to by the MCU via the CBUS.

The regulator **VCORE** is likewise adjustable and controlled by registers written by the MCU. VCORE supplies the core of the UPP and can be adjusted on the fly by the MCU if DSP capacity is inadequate. Higher VCORE supply (1.8 V) results in faster core operations in the UPP.

The regulator VFLASH2 supplies audio circuitry and is controlled by the MCU

Regulators VANA, VFLASH1 and VIO are solely controlled by the UEM and cannot be enabled or disabled by the MCU. Furthermore, VFLASH1 and VIO are both ON, though in low quiescent mode when phone is in sleep mode. An output current of 500  $\mu$ A can be drawn from the regulators. VIO supplies the UPP, FLASH and LCD, VFLASH1 supplies LCD and the IrDA module. VANA is supplying analogue parts internally in the UEM as well as the baseband audio circuitry and pull-up resistors on the input of the UEM slow AD converters.

System connector provides a voltage to supply accessories. The white LED's need a higher voltage supply as the battery can provide in bad condition. Separate external regulators

**CCS Technical Documentation**

supply both consumers.

The regulators VR1A, VR1B, VR2 - VR7 and IPA1 - IPA4 are controlled by the DSP via the DBus. VR4 - VR7 are controlled by the UEM as well and are disabled in sleep regardless of DSP writings.

VBAT is furthermore distributed, unregulated, to the RF power amplifier, audio power amplifier and external baseband regulators.

The CHACON module in the UEM controls the charging of the main battery. Furthermore it contains a 3.2 Vdc regulator for charging of the backup battery and a 1.8 Vdc regulator supplying the internal real time clock.

Figure 3: Baseband power distribution

# **DC Characteristics**

The following table reflects the specifications of voltage and current regulators within the UEM:

Output Voltage (V) **Output Current** Regulator **Target** (mA) Min Max Min Max Typ VR1A RF 4.6 4.75 4.9 0 10 RF 2.70 2.78 2.86 0.1 100 VR2<sup>4</sup> VR3 RF 2.70 2.78 2.86 0.1 20 VR4 RF 2.70 2.78 2.86 0.1 50 0.1 RF 2.70 2.78 2.86 0.1 50 VR5, VR61 0.1 VR7 RF 2.70 2.78 2.86 0.1 45 VrefRF01 RF 1.334 1.35 1.366 0.1 BB 1.72 1.8 150 VIO<sup>1</sup> 1.88 0.005 0.005 0.500 BB 1.745 1.8 1.855 0.005 25 VSIM<sup>2</sup> 2.91 3.0 3.09 0.005 0.500 **VANA** 2.70 2.78 BB 2.86 0.005 80 ВВ 1.000 1.053 0.005 70 1.106 VCORE<sup>2</sup> 1.235 1.3 1.365 0.005 85 1.425 1.5 1.575 0.005 100 1.710 1.8 1.890 0.005 120 0.974 1.053 70 200 1.132 1.215 1.3 1.365 85 200 1.5 1.575 100 200 1.410 1.692 1.8 1.890 120 200 VFLASH1 BB 2.70 2.78 0.005 70 2.86 0.005 1.5 ВВ 2.70 2.78 2.86 0.005 40 VFLASH23

Table 2: UEM regulator outputs

- 1 The second current value indicates the maximum possible output current of the regulator when in low guiescent mode.

- 2 The output voltages are split into two different current categories. The upper part is the lower range of output current, and the lower part is the higher range of output current.

- 3 Condition in sleep-mode depends on MCU writings to UEM regulator register solely.

- 4 Condition in sleep-mode depends on DSP writings to UEM register.

# Charging

The charging of the main battery is controlled by the UEM. External components are needed in order to sense charging current and voltage that are needed by the Energy Management (EM) software and to protect against EMC into the baseband area. The charger is connected to the phone via the DCT3 bottom connector or the charger pads of the Pop-port system connector.

Figure 4: Charging configuration

Connecting a charger to the telephone creates a voltage, VCH, on the UEM VCHAR input. When the VCH level is detected to rise above the VCH<sub>DET</sub> threshold (2.0 Vdc) by CHACON, charging starts.

3-wire chargers can be connected, but the PWM is not supported.

In order to protect the phone from damage due to over voltage caused by a sudden battery removal while charging proceeds, the charger switch is closed immediately.

# **Audio Circuitry**

This section describes the audio-HW inside the BB. Thus e.g. external audio components and acoustics are not considered with the details in this section.

The main topology comes from other phones using BB4.0 engine, where the audio-HW is mostly integrated into the UEM-ASIC. The biggest difference is that NPL-2 has also integrated hands-free (IHF).

# Audio Block Diagram

Figure 5: Audio Block Diagram

#### **Earpiece**

NPL-2 uses an earpiece which is also referred to as "PICO speaker". This is a 32 ohm speaker with the diameter of 8 mm.

Earpiece is fed by the differential signals "EARP" & "EARN" from UEM. The signals run quite directly from UEM to the earpiece, only some passive and EMC protection components are needed.

The external earpiece signals is fed by the "HF" & "HFCM" pins.

The level (swing) of earpiece-signals can be adjusted by register values inside UEM. These signals have common voltage level of 1.35 V (0.8 V for HF) at UEM pins.

# Microphones

An EMC-improved type of microphone is used as internal microphone in NPL-2, diameter of which is 2.2mm.

Internal Microphone circuitry is driven single ended. Microphone needs bias voltage, which is provided by UEM and is fed through a resistor to the microphone. A resistor is

6 - Baseband Description and Troubleshooting

also needed to other side of the microphone, i.e. between microphone and GND, in order to provide the differential signals to UEM. Audio signals are AC-coupled from the microphone.

For the external microphone a differential input is used.

MIC1N & MIC1P (audio signals) and MICB1 (bias voltage) are used for the internal microphone. MIC2N & MIC2P and MICB2 are used for external microphone.

# Integrated Hands-free (IHF)

The speaker used for IHF is a 16 mm diameter speaker with 8 Ohm impedance, and is also known as "MALT" speaker.

IHF circuitry uses differential outputs from UEM.

Depending on the audio mode the IHF amplifier is driven either from UEM HF / HFCM or XEAR audio outputs. The IHF audio power amplifier (APA) LM4890 has a bridge-tied-load (BTL) output in order to get the maximum use of supply voltage. The supply voltage for driving circuitry of speaker is VBAT, thus the swing across the speaker is (VBAT.

The shutdown of the IHF PA is controlled by UPP using GENIO14.

# **Audio Accessory Receive Path**

In NPL-2 the accessory receive path is directly driven from UEM HF / HFCM differential audio outputs, the output signal complies with the Pop-port accessory interface.

For EMC protection ferrites are connected in series to the earpiece, for ESD protection varistors are used.

#### **Audio Control Signals**

Furthermore, a couple of signals are needed to control the external audio device.

The HEADINT signal is needed for recognizing the external device (e.g. headset) connected to the system. The recognition is based on the ACI-pin on the system connector, which is shorted to ground inside the external device.

The button of the external device generates HOOKINT. This is used e.g. to answer or to end a phone call.

# **Acoustics**

# **Earpiece Acoustic**

NPL-2 uses the so called "PICO" earpiece.

This earpiece is mounted into the UI-shield assembly, the sealing of the back and front volume are implemented in the UI-shield by die casting. This sealing part also provides the sealing against the A-cover.

Figure 6: Earpiece implementation

# **IHF Speaker Acoustics**

As mentioned, the so called "MALT" speaker is used in NPL-2 for integrated hands-free and ringing tone applications.

The IHF speaker is mounted to the IHF enclosure by means of the speaker adhesive. The IHF enclosure provides the needed back volume for the speaker. The IHF enclosure is closed with the IHF lid, which is carrying the IHF pins to contact the IHF speaker.

The sealing of the effective acoustic volumes is achieved with the enclosure adhesive, which glues the IHF lid to the IHF enclosure.

To provide a long-term reliability additionally the IHF lid is heat stacked to the IHF enclosure.

The B-cover gasket provides a fitting between the B-cover and the IHF enclosure. This fitting is attached with an adhesive to the IHF enclosure and also includes a dust and water shield to protect the speaker inside from dust and swarf.

Due to the fact that the IHF enclosure is also carrying the antenna radiator, the whole assembly is named antenna assembly.

Due to heat stacking of the antenna assembly, it cannot be disassembled and in case of failure only be exchanged as one complete assembly.

Figure 7: Exploded View of Antenna Assembly

# **Microphone Acoustics**

A standard microphone module is used. This module is embedded into a so called "rubber boot" and connected to NPL-2 system module by spring contacts.

The microphone is placed close to the system connector. Tthe sound port of the microphone is located towards the bottom of the phone

#### Vibra Motor

A vibrating alerting device is used to generate a vibration signal for an incoming call.

This vibra is located in the bottom section of the phone.

The vibrator is driven by the UEM output VIBRA, and controlled with a PWM signal. The supply of the vibra is taken from the battery voltage of the phone.

# **Audio Modes**

There are six different audio configurations. These can create following audio modes:

- Hand portable

- Integrated hands-free

- Headset

- Loop set

- External hands-free

The following audio sources have to be routed according to the active audio mode:

- Speech

- Ringing tones / SMS tones

- Keypad tones

- Error tones / Warning tones

- Game tones

#### **Hand Portable Mode**

In hand portable mode earpiece path and internal microphone path are in use. The audio sources are routed according to the following table:

Table 3: Handportable mode audio routing

| Audio Source             | Earpiece | Earpiece Internal IHF Microphone speaker |   | Accessory receive path | Accessory transmit path |

|--------------------------|----------|------------------------------------------|---|------------------------|-------------------------|

| Speech                   | Х        | Х                                        |   |                        |                         |

| Ringing tones, SMS tones |          |                                          | Х |                        |                         |

| Keypad tones             | Х        |                                          |   |                        |                         |

| Warning / Error tones    |          |                                          | Х |                        |                         |

| Game tones               |          |                                          | Х |                        |                         |

# **Integrated Hands-free Audio Mode**

In integrated hands-free mode IHF path and internal microphone path are used. The audio sources are routed according to the following table:

Table 4: IHF mode audio routing

| Audio Source             | Earpiece | Internal<br>Microphone | IHF<br>speaker | Accessory receive path | Accessory transmit path |

|--------------------------|----------|------------------------|----------------|------------------------|-------------------------|

| Speech                   |          | Х                      | Х              |                        |                         |

| Ringing tones, SMS tones |          |                        | Х              |                        |                         |

| Keypad tones             |          |                        | Х              |                        |                         |

| Warning / Error tones    |          |                        | Х              |                        |                         |

| Game tones               |          |                        | Х              |                        |                         |

#### **Headset Audio Mode**

In headset mode accessory receive path and accessory transmit path are used. NPL-2 supports the following headsets:

HDB-4: Mono Headset, boom design HDC-xxx: Mono Headset, traditional design

The audio sources are routed according to the following table:

**Table 5:** Headset mode audio routing

| Audio Source             | Earpiece | Internal<br>Microphone | IHF<br>speaker | Accessory receive path | Accessory<br>transmit path |

|--------------------------|----------|------------------------|----------------|------------------------|----------------------------|

| Speech                   |          |                        |                | Х                      | Х                          |

| Ringing tones, SMS tones |          |                        | Х              | Х                      |                            |

**Table 5:** Headset mode audio routing

| Audio Source          | Earpiece | Internal<br>Microphone | IHF<br>speaker | Accessory receive path | Accessory transmit path |

|-----------------------|----------|------------------------|----------------|------------------------|-------------------------|

| Keypad tones          |          |                        |                | Х                      |                         |

| Warning / Error tones |          |                        |                | Х                      |                         |

| Game tones            |          |                        |                | Х                      |                         |

# **Loop set Audio Mode**

In loop set mode accessory receive path and accessory transmit path are used. NPL-2 supports the loop set LPS4.:

Table 6: Loop set mode audio routing

| Audio Source             | Earpiece | Internal<br>Microphone | IHF speaker | Accessory receive path | Accessory transmit path |

|--------------------------|----------|------------------------|-------------|------------------------|-------------------------|

| Speech                   |          |                        |             | Х                      | Х                       |

| Ringing tones, SMS tones |          |                        | Х           | Х                      |                         |

| Keypad tones             |          |                        |             | Х                      |                         |

| Warning / Error tones    |          |                        |             | Х                      |                         |

| Game tones               |          |                        |             | Х                      |                         |

#### External Hands-free Audio Mode

In external hands-free mode accessory receive path and accessory transmit path are used. NPL-2 supports external hands-free accessories:

BHF-1: basic car hands-free kit HFU-4: advanced car hands-free kit

**Table 7:** External hands-free mode audio routing

| Audio Source             | Earpiece | Internal<br>Microphone | IHF speaker | Accessory receive path | Accessory transmit path |

|--------------------------|----------|------------------------|-------------|------------------------|-------------------------|

| Speech                   |          |                        |             | Х                      | Х                       |

| Ringing tones, SMS tones |          |                        |             | Х                      |                         |

| Keypad tones             |          |                        |             | Х                      |                         |

| Warning / Error tones    |          |                        |             | Х                      |                         |

| Game tones               |          |                        |             | Х                      |                         |

# **User Interface**

# LCD module

NPL-2 is using a 130  $^{*}$  130 dot LCD display with 4096 colors. The illumination is integrated into the LCD module.

#### Baseband-LCD interface

The LCD display is connected to the transceiver PWB by 10-pin board-to-board connector.

Figure 8: LCD connector

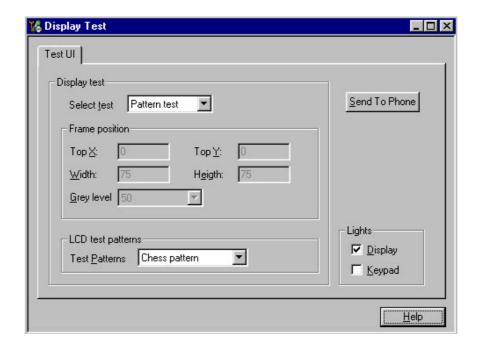

#### **DC Characteristics**

Display is using 3-wire serial interface. Signals for LCD panel are shown in table below.

The chip-select **XCS** (active low) enables and disables the serial interface. **RESX** (active low) is external reset signal. The **SCL** is serial data clock. **SI** data-length is 8 bits + **D/C**-bit. First bit is **D/C**-bit which indicates the status of following 8 bit data. In case of command data **D/C**-bit is low ('0'). **VDDI** is logic voltage supply for the display. **VDD** is supply voltage for high voltage generation. **GND** is system ground for display.

Table 8: LCD Interface DC Characteristics

Description Min Typical Max L

| Pin No | Signal name | Description | Min                 | Typical | Max                    | Unit | Description                 |

|--------|-------------|-------------|---------------------|---------|------------------------|------|-----------------------------|

| 1      | VDDI        | IN          | 1.7                 | 1.8     | VDD                    | V    | Logic voltage supply        |

| 2      | RESX        | IN          | H: 0.7xVDD<br>L: 0  |         | H: VDDI<br>L: 0.3xVDDI | V    | Reset<br>(active low)       |

| 3      | SI          | IN          | H: 0.7xVDDI<br>L: 0 |         | H: VDDI<br>L: 0.3xVDDI | V    | Serial input                |

| 4      | SCL         | IN          | H: 0.7xVDDI<br>L: 0 |         | H: VDDI<br>L: 0.3xVDDI | V    | Serial input clock          |

|        |             |             |                     |         | 6.5                    | MHz  | Serial data clock speed     |

| 5      | XCS         | IN          | H: 0.7XVDDI<br>L: 0 |         | H: VDDI<br>L: 0.3xVDDI | V    | Chip select<br>(Active low) |

| 6      | VDD         | IN          | 2.6                 | 2.75    | 3.6                    | V    | Voltage supply              |

| 7      | NC          |             |                     | 0       |                        | V    | Not connected               |

| 8      | GND         |             |                     |         |                        |      | System ground               |

| 9      | LED -       |             | 0.505               | 0.525   | 0.545                  | V    |                             |

| 10     | LED +       |             | TBD                 | 7.0     | TBD                    | V    |                             |

(Note: H stands for high signal level and L for low signal level.)

# **Current Consumption**

Table 9: LCD Interface Current Consumption

| Pin<br>No. | Signal name | Description          | Min | Typical | Max  | Unit | Description                                                              |

|------------|-------------|----------------------|-----|---------|------|------|--------------------------------------------------------------------------|

| 6/8        | VDD         | Display pixels       | -   | 0.5     | 1.25 | mA   | Full mode, 4 k colors. Maximum for chess pattern picture.                |

| 6/8        | VDD         | Display pixels       | -   | 0.15    | 0.25 | mA   | Partial mode, 32 lines, 4 k colors.<br>Maximum for chess pattern picture |

| 9/10       | LED - LED + | Display illumination | -   | 15      | 30   | mA   | 2 white LED in series                                                    |

# **Maximum Ratings**

Table 10: LCD Interface Maximum Ratings

| Item                         | Symbol           | Rating             | Unit |

|------------------------------|------------------|--------------------|------|

| Power Supply voltage         | $V_{DD}$         | -0.3 to + 4.0      | V    |

| Power supply voltage (logic) | V <sub>DDI</sub> | -0.3 to + 4.0      | V    |

| Signal Input voltage         | V <sub>IN</sub>  | -0.3 to Vddi + 0.5 | V    |

| LED input current            | I <sub>LED</sub> | 30                 | mA   |

# **AC Characteristics**

Figure 9: Write characteristics

Table 11: AC characteristics

| Signal | Symbol            | Parameter                | Min | Max | Unit |

|--------|-------------------|--------------------------|-----|-----|------|

| CSX    | T <sub>CSS</sub>  | Chip select setup time   | 10  | -   | ns   |

|        | T <sub>CSH</sub>  | Chip select hold time    | 35  | 1   | ns   |

| SCL    | t <sub>SCYC</sub> | Clock cycle              | 150 | ı   | ns   |

|        | t <sub>SLW</sub>  | Clock pulse "L" duration | 60  | -   | ns   |

|        | t <sub>SHW</sub>  | Clock pulse "H" duration | 60  | 1   | ns   |

Table 11: AC characteristics

| Signal | Symbol           | Parameter       | Min | Max | Unit |

|--------|------------------|-----------------|-----|-----|------|

| SI     | T <sub>SDS</sub> | Data setup time | 60  | -   | ns   |

|        | T <sub>SDH</sub> | Data hold time  | 60  | -   | ns   |

- 1. Rise tr and fall tf time must be within 15 ns maximum.

- 2. Timings are specified according to 30% and 70% of  $V_{DDI}$  as reference. Definitions to rise and fall times are described in the figure below.

Figure 10: Rise and fall time in input and output

Table 12: Rise and fall times in input and output of display driver

| Parameter | Symbol | Min | Max | Unit |

|-----------|--------|-----|-----|------|

| Input     | Tr, tf |     | 15  | ns   |

| Output    | Tr, tf |     | 15  | ns   |

# **Reset Timing**

Reset timing characteristics are shown in the figure below.

Figure 11: Reset timing

Table 13: Reset Timing

| Signal | Symbol | Parameter            | Min | Max  | Unit |

|--------|--------|----------------------|-----|------|------|

| RESX   | tRW    | Reset pulse duration | 200 |      | ns   |

|        | tRT    | Reset cancel         |     | 1500 | ns   |

# Display Power On/Off Sequence

Power on/off sequence if described in the figure below

Figure 12: Power on/off Sequence

# **LED Power Supply**

In NPL-2, white LED are used for LCD and pastel blue LED for keypad lighting. Two LED are used for LCD lighting and eight LED for keyboard. A step up DC-DC converter TK11851 is used as a LED driver.

The display LEDs are driven in serial mode to achieve stable backlight quality. This means constant current flow through LCD LEDs. Serial resistance R\_lcd is used to define the proper current. The feedback signal, FB, is used to control the current. Driver will increase or decrease the output voltage for LEDs to keep the current stable.

Keyboard LED are driven in 2 serial/4 parallel mode. This means constant current flow through each branch. Serial resistance R are used to limit the current through LEDs.

Driver is controlled by the UEM via the DLIGHT open drain output (internal pull up active). This signal is connected to driver EN-pin. It is possible to control the LED brightness by PWM.

# Keypad

The NPL-2 phone doesn't have separate keyboard PCB. The keys are directly connected via the KEYB(10:0) bus to the UPP. The keypad consist of a 5x4 matrix, meaning 5 rows (ROWO - ROW4) and 4 columns (COL1 - COL4).

Figure 13: NPL-2 keypad

Figure 14: Side (volume) keys

When there is no key pressed, all the inputs from the rows are high due to that the UPP has internally pull-up resistors on those lines. All the columns are low at this state. When a key is pressed, the specific row where the key is placed is pulled low. This generates an interrupt to the MCU and the MCU now starts its scanning procedure. The procedure first set all the columns high (KEYB (0) to KEYB (4)) and then one by one set them low again. Only one of the columns is low at the time. While one of the columns is low, the row is (KEYB (5) to KEYB (10)) is read by MCU to find the active low signal. If the input is low the MCU knows that a key is pressed. When the key has been detected all the keypadregister inside the UPP is reset and it's ready receiving new interrupt.

The power on key is connected to the UEM PWRONX signal.

# SIM Interface

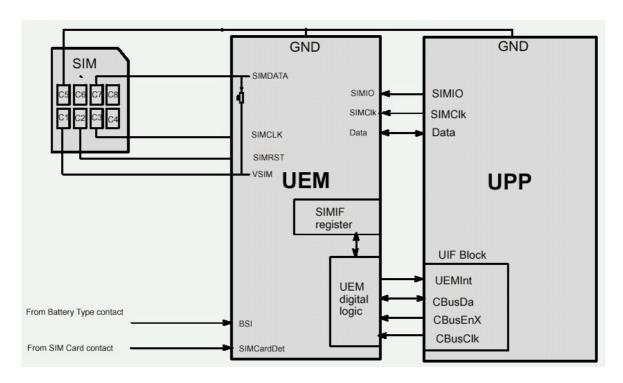

NPL-2 uses a product specific SIM-card reader (SIM reader). Electrical connection of SIM reader is similar to other DCT4 products.

The SIM interface is split between UEM and UPP (see figure below). This has been done in order to reduce the amount of interconnections on the SIM interface between the UPP and the UFM.

The SIM interface control logic and UART is integrated into the UPP. The SIM interface start-up and power down sequence, including timing and reset generation is implemented in UEM. The SIM interface in the UPP supports the SIM speed enhancement features, which improves the data transfer rate in the SIM interface.

The UEM contains the SIM interface logic level shifting. UPP SIM interface logic levels are 1.8V. The SIM interface can be programmed to support 3V and 1.8V SIMs. A 5V SIM interface is not supported. A register in the UEM selects the SIM supply voltage. It is only allowed to change the SIM supply voltage when the SIM IF is powered down.

The SIM power up/down sequence is generated in the UEM. The Battery Type contact signal (BSI) is used to recognize if the battery suddenly is removed from the transceiver block. The SIMCardDet is not used. If the BSI goes low, the power down sequence is automatic initiated. The SIMIF will then force all the connections low, i.e. SIMRST, SIMCLK, SIMDATA and VSIM. A comparator inside the UEM does the monitoring of the BSI signal. The comparator offset is such that the comparator output does not alter state as long as the battery is connected. The BSI comparator threshold level is 2.1 V with 75 mV hysteresis.

Figure 15: UPP, UEM and SIM Connections

# **BB-RF** Interface

The below table describes all the signals from the baseband block to the RF block and back. The signal names are based on the schematics.

# Digital Signals between BB and RF

For the digital interfaces UPP and Mjoelner use only level shifting IO. Level shifters of both are supplied with VIO from UEM. VIO limits are specified in chapter 0 and have been used to calculate the limits below (because  $VIO_{min}$  is 1.72V this was used for UPP  $V_{DDS_{min}}$  and not the limit from UPP which would have been 1.26V).

Values are refenced to GND unless otherwise specified.

Table 14: RF-BB Interface Digital Signals

| Signal name              | From                  | То                          | Pa        | arameter                                                     | Min                          | Тур | Max          | Unit        | Notes                               |

|--------------------------|-----------------------|-----------------------------|-----------|--------------------------------------------------------------|------------------------------|-----|--------------|-------------|-------------------------------------|

| RFICCNTRL (2             | RFICCNTRL (2:0)       |                             |           | control bus                                                  |                              |     | •            |             |                                     |

| RFBUSEN1<br>RFICCNTRL(2) | UPP<br>RFBUSEN1X      | <b>Mjoelner</b><br>RFBUSENX | Logic "1" | Mjoelner input<br>UPP output                                 | 1.22<br>1.37                 |     | 1.88         | V<br>V      | RF Chip select.<br>Active Low       |

|                          |                       |                             | Logic "0" | Mjoelner input<br>UPP output                                 | 0<br>0                       |     | 0.4<br>0.40  | V<br>V      |                                     |

| RFBUSDA<br>RFICCNTRL(1)  | <b>UPP</b><br>RFBUSDA | <b>Mjoelner</b><br>RFBUSDA  | Logic "1" | Mjoelner input<br>UPP output<br>Mjoelner output<br>UPP input | 1.22<br>1.37<br>1.32<br>1.32 |     | 1.88<br>1.88 | V<br>V<br>V | RF serial data.<br>(bi-directional) |

Table 14: RF-BB Interface Digital Signals

| Signal name  | From     | То        | Pa                  | arameter                     | Min  | Тур | Max  | Unit        | Notes                    |

|--------------|----------|-----------|---------------------|------------------------------|------|-----|------|-------------|--------------------------|

| RFBUSDA      | UPP      | Mjoelner  | Logic "0"           | Mjoelner input               | 0    |     | 0.4  | V           | RF serial data.          |

| RFICCNTRL(1) | RFBUSDA  | RFBUSDA   |                     | UPP output                   | 0    |     | 0.40 | V           | (bi-directional)         |

|              |          |           |                     | Mjoelner output<br>UPP input | 0    |     | 0.4  | V           |                          |

|              |          |           |                     | orr input                    | 0    |     | 0.51 | V           |                          |

| RFBUSCLK     | UPP      | Mjoelner  | Logic "1"           | Mjoelner input               | 1.22 |     |      | V           | RF bus clock.            |

| RFICCNTRL(0) | RFBUSCLK | RFBUSCLK  |                     | UPP output                   | 1.37 |     | 1.88 | V           |                          |

|              |          |           | Logic "0"           | Mjoelner input               | 0    |     | 0.4  | V           |                          |

|              |          |           |                     | UPP output                   | 0    |     | 0.40 | V           |                          |

|              |          |           | Clock Spe           | eed                          |      | 13  |      | MHz         |                          |

| GENIO (28:0) |          | 1         | General purpose I/O |                              |      |     |      |             |                          |

| TXP          | UPP      | Mjoelner  | Logic "1"           | Mjoelner input               | 1.22 |     |      | V           | Transmitter              |

| GENIO(5)     | GENIO5   | TXP       |                     | UPP output                   | 1.37 |     | 1.88 | V           | power control<br>enable. |

|              |          |           | Logic "0"           | Mjoelner input               | 0    |     | 0.4  | V           | enable.                  |

|              |          |           |                     | UPP output                   | 0    |     | 0.40 | V           |                          |

| RESET        | UPP      | Mjoelner  | Logic "1"           | Mjoelner input               | 1.22 |     |      | V           | Reset to RF              |

| GENIO(6)     |          | RESET     | SET                 | UPP output                   | 1.37 |     | 1.88 | V           | chip.<br>Active low.     |

|              | L        | Logic "0" | Mjoelner input      | 0                            |      | 0.4 | V    | Active low. |                          |

|              |          |           |                     | UPP output                   | 0    |     | 0.40 | V           |                          |

# Analog Signals between BB and RF

The values indicated in the table below are input requirements of the device in the "to column" when nothing else is stated. Values are refenced to GND unless other wise specified.

**Table 15:** RF-BB-Interface Aanlog Signals

| Signal name         | From                    | То                   | Parameter                  | Min                      | Тур  | Max    | Unit | Notes                                      |  |

|---------------------|-------------------------|----------------------|----------------------------|--------------------------|------|--------|------|--------------------------------------------|--|

| Clock               |                         |                      | System clock for phone     | System clock for phone   |      |        |      |                                            |  |

| RFCLK               | Mjoelner                | UPP                  | Frequency                  |                          | 26   |        | MHz  | System clock                               |  |

|                     | REFOUT                  | RFCLK                |                            | -20                      |      | +20    | ppm  | 1                                          |  |

|                     |                         |                      | Duty cycle                 | 40                       |      | 60     | %    |                                            |  |

|                     |                         |                      | Signal amplitude           | 0.3                      |      | 1.32   | Vpp  | Upp input req.                             |  |

|                     |                         |                      | Setling time               |                          |      | 5.0    | ms   | VR3 on to sta-<br>ble clock @<br>UPP input |  |

| RFCONV (9:0)        |                         | •                    | RF / BB analogue signa     | RF / BB analogue signals |      |        |      |                                            |  |

| RXIINP<br>RFCONV(0) | <b>Mjoelner</b><br>RXIP | <b>UEM</b><br>RXIINP | Max input<br>Voltage swing | 1.35                     | 1.4  | 1.45   | Vpp  | Differential complex RX BB                 |  |

| RXIINN              | Mjoelner                | UEM                  | Nominal Voltage swing      |                          |      |        | V    | signal                                     |  |

| RFCONV(1)<br>RXQINP | RXIM<br><b>Mjoelner</b> | RXIINN<br><b>UEM</b> | Input DC level             | 1.3                      | 1.35 | 1.4    | Vdc  | -                                          |  |

| RFCONV(2)           | RXQP                    | RXQINP               | Signal frequency           |                          | 67,7 |        | KHz  | 1                                          |  |

| RXQINN<br>RFCONV(3) | <b>Mjoelner</b><br>RXQM | <b>UEM</b><br>RXQINN | Input BW                   |                          |      | 270.83 | KHz  |                                            |  |

**Table 15:** RF-BB-Interface Aanlog Signals

| Signal name                     | From                  | То                      | Parameter                                  | Min        | Тур            | Max           | Unit              | Notes                          |  |

|---------------------------------|-----------------------|-------------------------|--------------------------------------------|------------|----------------|---------------|-------------------|--------------------------------|--|

| TXIOUTP<br>RFCONV(4)            | <b>UEM</b><br>TXIOUTP | <b>Mjoelner</b><br>TXIP | Max Differential output swing (ref. TxIN)  | 2.15       | 2.2            | 2.25          | Vpp               | Differential complex TX        |  |

| TXIOUTN<br>RFCONV(5)<br>TXQOUTP | TXIOUTN<br>UEM        | Mjoelner<br>TXIN        | Input diff. Swing<br>(ref. TxIN)           |            | 1.0            |               | Vpp               | signal (pro-<br>gramable volt- |  |

| RFCONV(6)                       | TXQOUTP               | <b>Mjoelner</b><br>TXQP | DC level                                   | 1.0        | 1.1            | 1.25          | Vdc               | age swing)                     |  |

| TXQOUTN                         | UEM                   | Mjoelner                | Source impedance                           |            |                | 200           | Ω                 |                                |  |

| RFCONV(7)                       | TXQOUTN               | TXQN                    | Signal frequency                           |            | 67,7           |               | KHz               |                                |  |

| RFAUXCONV(2                     | 2:0)                  | •                       | RF / BB analogue control signals           |            |                |               |                   |                                |  |

| TXC<br>RFAUXCONV(0)             | <b>UEM</b><br>AUXOUT  | <b>Mjoelner</b><br>TXC  | Output voltage                             | 0 -<br>0.1 |                | 2,4 -<br>2.55 | V                 | Transmitter power control      |  |

|                                 |                       |                         | Source impedance                           |            |                | 200           | Ω                 |                                |  |

|                                 |                       |                         | Resolution                                 | 1          | 0              |               | Bits              |                                |  |

|                                 |                       |                         | Reference                                  |            | kref<br>F01 ?) |               |                   |                                |  |

|                                 |                       |                         | Power coef. Range.                         | 0,05       |                | 0,94          | Vtxc/<br>Vtxc_max |                                |  |

|                                 |                       |                         | Recom. Power Coef.1 @<br>pwr.lvl.5 (0 pcn) | 0,7        |                | 0,9           | Vtxc/<br>Vtxc_max |                                |  |

|                                 |                       |                         | Recom.Power Coef. @<br>pwr.lvl.19 (15 pcn) | 0,1        |                | 0,2           | Vtxc/<br>Vtxc_max |                                |  |

|                                 |                       |                         | Recom.Power Coef @ Base level              | 0,1        |                | 0,2           | Vtxc/<br>Vtxc_max |                                |  |

# Voltage Regulators in BB for RF

Values are refenced to GND unless otherwise specified.

**Table 16:** Voltage Supplies and References

| Signal name | From | То       | Parameter               | Min  | Тур                 | Max  | Unit | Notes           |

|-------------|------|----------|-------------------------|------|---------------------|------|------|-----------------|

| Regulators  | •    | •        | RF regulators           |      | •                   |      |      |                 |

| VR1A        | UEM  | Mjoelner | UEM Output Voltage      | 4.6  | 4.75                | 4.9  | V    | Supply to:      |

|             | VR1A | VDDCP    | Mjoelner Input Voltage  | 2.64 | 2.78                | 4.9  | V    | Charge pump     |

|             |      |          | UEM output Load Current | 0    | (3)                 | 5    | mA   | ]               |

|             |      |          | UEM Load Capacitance    | 800  | 1000                | 1200 | nF   | 1               |

|             |      |          |                         | 20   |                     | 600  | mΩ   | ESR             |

|             |      |          | Settling Time           |      | 300+t <sub>d2</sub> |      | μs   | Sleep to Active |

| VR2         | UEM  | Mjoelner | UEM Output Voltage      | 2.70 | 2.78                | 2.86 | V    | Supply to TX -  |

|             | VR2  | VDDTX    | Mjoelner Input Voltage  | 2.64 | 2.78                | 2.86 | V    | chain Modula-   |

|             |      | VDDDIG   | Load Current            | 0.1  | 3)                  | 100  | mΑ   | tor digital     |

|             |      |          | Load Capacitance        | 800  | 1000                | 1200 | nF   | contl logic     |

|             |      |          |                         |      |                     |      |      |                 |

|             |      |          |                         | 20   |                     | 600  | mΩ   | ESR             |

|             |      |          | Settling Time           | 10   |                     |      | μs   | Sleep to Active |

**Table 16:** Voltage Supplies and References

| Signal name | From              | То                          | Parameter                             | Min   | Тур  | Max              | Unit      | Notes                                      |

|-------------|-------------------|-----------------------------|---------------------------------------|-------|------|------------------|-----------|--------------------------------------------|

| VR3         | <b>UEM</b><br>VR3 | Mjoelner<br>VDDXO<br>VDDBBB | UEM Output Voltage                    | 2.70  | 2.78 | 2.86             | V         | Supply to :<br>XO and base-<br>band buffer |

|             |                   |                             | Mjoelner Input Voltage                | 2.64  | 2.78 | 2.86             | V         |                                            |

|             |                   |                             | Load Current                          | 0.1   | (3)  | 20               | mA        |                                            |

|             |                   |                             | Load Capacitance                      | 800   | 1000 | 1200             | nF        |                                            |

|             |                   |                             |                                       | 20    |      | 600              | mΩ        | ESR                                        |

|             |                   |                             | Settling Time                         |       |      | 50               | μs        | Off to on                                  |

|             |                   |                             |                                       | 10 ?  |      |                  | μs        | Sleep to Active                            |

| VR4         | UEM               | Mjoelner                    | UEM Output Voltage                    | 2.70  | 2.78 | 2.86             | V         | Supply to:                                 |

|             | VR4               | VDD?RXBB                    | Mjoelner Input Voltage                | 2.64  | 2.78 | 2.86             | V         | RX baseband                                |

|             |                   |                             | Load Current                          | 0.1   | (3)  | 100              | mA        | section                                    |

| VR5         | UEM               | Mjoelner                    | UEM Output Voltage                    | 2.70  | 2.78 | 2.86             | V         | Supply to :                                |

|             | VR5               | VDDPRE                      | Mjoelner Input Voltage                | 2.64  | 2.78 | 2.86             | V         | Prescaler, devi-                           |

|             |                   | VDDLO                       | Load Current                          | 0.1   | (3)  | 50               | mA        | ders,                                      |

|             |                   | VDDPLL                      | Load Capacitance                      | 800   | 1000 | 1200             | nF        | LO buffers, PLL                            |

|             |                   |                             |                                       |       |      | (4)              |           | counters                                   |

|             |                   |                             | C Ti                                  | 20    |      | 600              | mΩ        | ESR                                        |

| \/D.o.      | 11584             | - I                         | Settling Time                         | 10    | 0.70 | 0.00             | μs        | Sleep to Active                            |

| VR6         | UEM               | Mjoelner                    | UEM Output Voltage                    | 2.70  | 2.78 | 2.86             | V         | Supply to :                                |

|             | VR6               | VDDRXF                      | Mjoelner Input Voltage                | 2.64  | 2.78 | 2.86             | V         | RX frontend                                |

|             |                   |                             | Load Current                          | 0.1   | (3)  | 50               | mA        | 1                                          |

|             |                   |                             | Load Capacitance                      | 800   | 1000 | 1200             | nF        |                                            |

|             |                   |                             |                                       | 20    |      | 600              | $m\Omega$ | ESR                                        |

|             |                   |                             | Settling Time                         | 10    |      |                  | μs        | Sleep to Active                            |

| VR7         | UEM               | VCO                         | UEM Output Voltage                    | 2.70  | 2.78 | 2.86             | V         | Supply to:                                 |

|             |                   |                             | VCO supply voltage range <sup>2</sup> | 2.55  | 2.78 | 2.85             | V         | VCO                                        |

|             |                   |                             | Load Current                          | 0.1   | (3)  | 45               | mA        | +                                          |

|             |                   |                             | Load Capacitance                      | 800   | 1000 | 1200             | nF        | +                                          |

|             |                   |                             | Loud Capacitance                      | 000   | 1000 | 1200             | '''       |                                            |

|             |                   |                             |                                       | 20    |      | 600              | mΩ        | ESR                                        |

|             |                   |                             | Settling Time                         | 10    |      |                  | μs        | Sleep to Active                            |

| VIO         | UEM               | Mjoelner                    | UEM Output Voltage                    | 1.72  | 1.88 | 1.88             | V         | Supply to:                                 |

|             | VI0               | VDDDL                       | Mjoelner Input Voltage                | 1.71  | 1.8  | 1.88             | V         | RF-BB inter-                               |

|             |                   |                             | Load Current                          | 0.1   | (3)  | 5 <sup>(3)</sup> | mΑ        | face level                                 |

|             |                   |                             | Load Capacitance                      |       |      |                  |           | shifter                                    |

|             |                   |                             | Settling Time                         | † †   |      |                  |           |                                            |

| References  |                   | -                           | RF References                         |       |      |                  | !         |                                            |

| VREF1       | UEM               | Mjoelner                    | UEM Output Voltage                    | 1.334 | 1.35 | 1.366            | V         | Used inside                                |

|             | VREF01            | VBEXT                       | Mjoelner Input Voltage                | 1.325 | 1.35 | 1.375            | V         | MJOELNER as                                |

|             |                   |                             | Load Current                          |       | (3)  | 100              | mA        | 1.35V refer-                               |

|             |                   |                             | Load Capacitance                      | 800   | 1000 | 1200             | nF        | ence                                       |

|             |                   |                             | Settling Time                         | † †   |      |                  | μs        | Sleep to Active                            |

# **System Connector Interface**

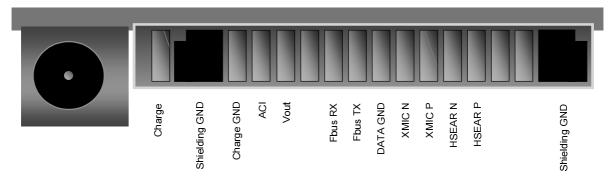

# **System Connector**

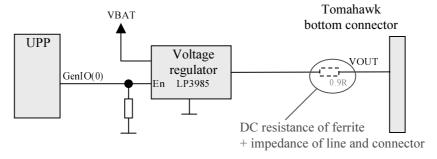

The system connector in NPL-2 (and several other DCT-4 products) is called Pop-Port System Connector (unofficial name: "Tomahawk"). It is a galvanic interface between phone and accessories.

Compared with previous system connector versions, four new functions are introduced with the Pop-port system connector interface:

- Accessory Control Interface (ACI)

- Power Out

- Stereo audio output

- Universal Serial Bus (USB).

USB functionality and stereo audio output of the Pop-port are not supported in NPL-2.

Note: MBUS function, (included in previous accessory interfaces, e.g. DCT-3) is no more supported by Pop-port interfaces.

Pop-port system connector is **mechanically and electrically not backward compatible** with any earlier Nokia accessory interfaces, except the charger connector.

Figure 16: Pop Port System Connector

**Table 17:** System connector interface description

| Pin # | Signal  | Notes                                                                  |

|-------|---------|------------------------------------------------------------------------|

| 1     | VCHAR   |                                                                        |

| 2     | GND     | Charge ground                                                          |

| 3     | ACI     | Insertion & removal detection /<br>Serial data bi-directional 1 kbit/s |

| 4     | Vout    |                                                                        |

| 5     |         | Not used in NPL-2                                                      |

| 6     | FBUS_RX | Serial data from accessory to phone / 115 kbit/s                       |

| 7     | FBUS_TX | Serial data from phone to accessory / 115 kbit/s                       |

| 8     | GND     | Data ground                                                            |

| 9     | XMIC N  | Negative audio in signal                                               |

| 10    | XMIC P  | Positive audio in signal                                               |

**Table 17:** System connector interface description

| Pin # | Signal  | Notes                                                      |

|-------|---------|------------------------------------------------------------|

| 11    | HSEAR N | Negative audio out signal.<br>Max bandwidth from the phone |

| 12    | HSEAR P | Positive audio out signal. Max bandwidth from the phone    |

| 13    |         | Not used in NPL-2                                          |

| 14    |         | Not used in NPI -2                                         |

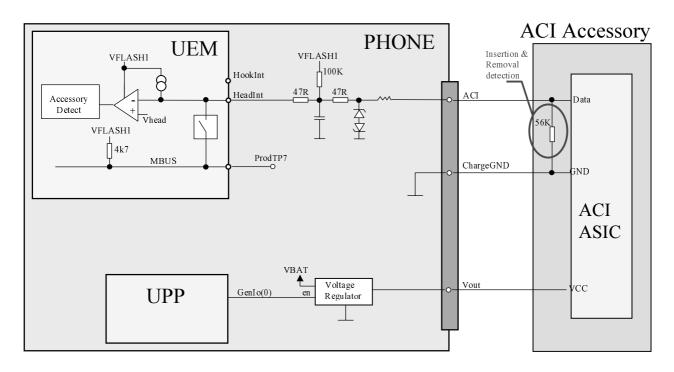

# Accessory Control Interface (ACI)

ACI is a point-to-point, master-slave, and bi-directional serial bus. It has three features:

- The insertion and removal detection of an accessory device

- Acting as a data bus, intended mainly for control purposes

- The identification and authentication of accessory type which is connected

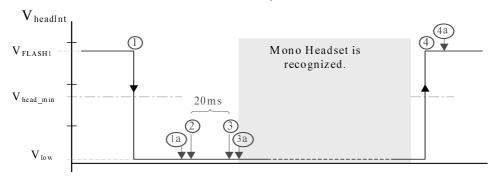

The accessories are detected by the HeadInt signal when the plug is inserted.

Normally when no plug is present, the pull-up resistor 100k pulls up the HeadInt signal to VFLASH1. If the accessory is inserted, the external "insertion & removal" resistor works as voltage divider and decrease the voltage level below the threshold Vhead.

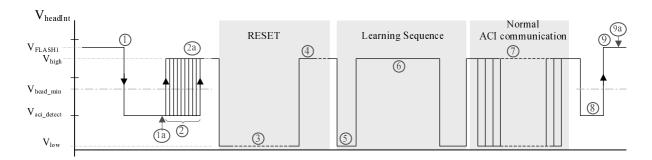

Thereby the comparator output will be changed to high state causing an interrupt.